**НУКУССКИЙ ФИЛИАЛ ТАШКЕНТСКИЙ УНИВЕРСИТЕТ

ИНФОРМАЦИОННЫХ ТЕХНОЛОГИИ ИМЕНИ МУХАММАДА

АЛ-ХОРАЗМИЙ**

**КУРС ЛЕКЦИЙ ПО ПРЕДМЕТУ

СИСТЕМЫ РЕАЛЬНОГО ВРЕМЕНИ. ВНЕШНИЕ СИСТЕМЫ.

1-часть**

**Составил:**

**Ф.М.Зарипов**

# Оглавление

|                                                                                                                                                            |           |

|------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| <b>Глава-I. Введение. Основные понятия систем реального времени.....</b>                                                                                   | <b>3</b>  |

| Лекция 1.1. Основные понятия систем реального времени. Структура, состав и основные технические и технологические показатели систем реального времени..... | 3         |

| <b>Глава-II. Контроль и управления в системах реального времени .....</b>                                                                                  | <b>12</b> |

| Лекция 2.1. Задачи контроля и управления, типы объектов, обработка и порядок работы управления систем реального времени.....                               | 12        |

| <b>Глава-III. СРЕДСТВА ПЕРЕРАБОТКИ ИНФОРМАЦИИ.....</b>                                                                                                     | <b>17</b> |

| Лекция 3.1. Классификация вычислительных систем. Многомашинные вычислительные системы.....                                                                 | 17        |

| Лекция 3.2. Многопроцессорные вычислительные системы. Кластеры.....                                                                                        | 23        |

| <b>ГЛАВА-IV. ПРОЦЕССОРЫ .....</b>                                                                                                                          | <b>31</b> |

| Лекция 4.1. Архитектура процессоров.....                                                                                                                   | 31        |

| Лекция 4.2. Организация данных во внешней памяти. Процессоры Motorola 68xxx. ....                                                                          | 42        |

| Лекция 4.3. Процессоры Intel 80x86, PowerPC. ....                                                                                                          | 49        |

| Лекция 4.4. Процессоры SPARC, Intel 80960x, ARM. ....                                                                                                      | 59        |

| <b>ГЛАВА-V. ШИНЫ.....</b>                                                                                                                                  | <b>71</b> |

| Лекция 5.1. Архитектура шинных систем. Архитектура шины (VME, PCI). ....                                                                                   | 71        |

# ГЛАВА-1. ВВЕДЕНИЕ. ОСНОВНЫЕ ПОНЯТИЯ СИСТЕМ РЕАЛЬНОГО ВРЕМЕНИ

## ЛЕКЦИЯ 1.1. ОСНОВНЫЕ ПОНЯТИЯ СИСТЕМ РЕАЛЬНОГО ВРЕМЕНИ. СТРУКТУРА, СОСТАВ И ОСНОВНЫЕ ТЕХНИЧЕСКИЕ И ТЕХНОЛОГИЧЕСКИЕ ПОКАЗАТЕЛИ СИСТЕМ РЕАЛЬНОГО ВРЕМЕНИ.

---

### План

- Основные понятия

- Структура СРВ

- ОСРВ и ОС общего назначения

- Механизмы реального времени

- Часы и таймеры

### Основные понятия

Существует несколько определений систем реального времени (СРВ), большинство из которых противоречат друг другу. Приведем несколько из них, чтобы продемонстрировать различные взгляды на назначение и основные задачи СРВ.

1. Системой реального времени называется система, в которой успешность работы любой программы зависит не только от ее логической правильности, но от времени, за которое она получила результат. Если временные ограничения не удовлетворены, то фиксируется сбой в работе системы.

Таким образом, временные ограничения должны быть гарантировано удовлетворены. Это требует от системы быть предсказуемой, т.е. вне зависимости от своего текущего состояния и загруженности выдавать нужный результат за требуемое время. При этом желательно, чтобы система обеспечивала как можно больший процент использования имеющихся ресурсов.

2. Стандарт POSIX 1003.1 определяет СРВ следующим образом: «Реальное время в операционных системах – это способность операционной системы обеспечить требуемый уровень сервиса в заданный промежуток времени».

3. Иногда системами реального времени называются системы постоянной готовности (on-line системы), или «интерактивные системы с достаточным временем реакции». Обычно это делают по маркетинговым соображениям. Действительно, если интерактивную программу называют работающей в «реальном времени», то это просто означает, что она успевает обработать запросы от человека, для которого задержка в сотни миллисекунд даже незаметна.

4. Иногда понятие «система реального времени» отождествляют с понятием «быстрая система». Это не всегда правильно. Время задержки СРВ на событие не так уж важно (оно может достигать нескольких секунд). Главное, чтобы это время было достаточно для рассматриваемого приложения и гарантировано. Очень часто алгоритм с гарантированным временем работы менее эффективен, чем алгоритм, таким действием не обладающий. Например, алгоритм «быстрой» сортировки в среднем работает значительно быстрее других алгоритмов сортировки, но его гарантированная оценка сложности значительно хуже.

5. Во многих сферах приложения СРВ вводят свои понятия «реального времени». Например, процесс цифровой обработки сигнала называют идущим в «реальном времени», если анализ (при вводе) и/или генерация (при выводе) данных может быть проведен за то же время, что и анализ и/или генерация тех же данных без цифровой обработки сигнала. Например, если при обработке аудио данных требуется 2.01 секунд для анализа 2.00 секунд звука, то это не процесс реального времени. Если же требуется 1.99 секунд, то это процесс реального времени.

**Назовем системой реального времени** аппаратно-программный комплекс, реагирующий в предсказуемые времена на непредсказуемый поток внешних событий

Это определение означает, что:

- Система должна успеть отреагировать на событие, произошедшее на объекте, в течение времени, критического для этого события (meet deadline). Величина критического времени для каждого события определяется объектом и самим событием, и, естественно, может быть разной, но время реакции системы должно быть предсказано (вычислено) при создании системы. Отсутствие реакции в предсказанное время считается ошибкой для систем реального времени.

- Система должна успевать реагировать на одновременно происходящие события. Даже если два или больше внешних событий происходят одновременно, система должна успеть среагировать на каждое из них в течение интервалов времени, критического для этих событий.

Хорошим примером задачи, где требуется СРВ, является управление роботом, берущим деталь с ленты конвейера. Деталь движется, и робот имеет лишь маленькое временное окно, когда он может ее взять. Если он опаздывает, то деталь уже не будет на нужном участке конвейера, и, следовательно, работа не будет сделана, несмотря на то, что робот находится в правильном месте.

Если он позиционируется раньше, то деталь еще не успеет подъехать, и робот заблокирует ей путь. Другим примером может быть самолет, находящийся на автопилоте. Сенсорные серводатчики должны постоянно передавать в управляющий компьютер результаты измерений. Если результат какого-либо измерения будет пропущен, то это может привести к недопустимому несоответствию между реальным состоянием систем самолета и информацией о нем в управляющей программе.

Различают системы реального времени двух типов - системы жесткого реального времени и системы мягкого реального времени.

**Системы жесткого реального времени** не допускают никаких задержек реакции системы ни при каких условиях, так как:

- результаты могут оказаться бесполезны в случае опоздания,

- может произойти катастрофа в случае задержки реакции,

- стоимость опоздания может оказаться бесконечно велика.

Примеры систем жесткого реального времени - бортовые системы управления, системы аварийной защиты, регистраторы аварийных событий.

**Системы мягкого реального времени** характеризуются тем, что задержка реакции не критична, хотя и может привести к увеличению стоимости результатов и снижению производительности системы в целом.

Пример - работа сети. Если система не успела обработать очередной принятый пакет, это приведет к таймауту на передающей стороне и повторной посылке (в зависимости от протокола, конечно). Данные при этом не теряются, но производительность сети снижается.

Основное отличие между системами жесткого и мягкого реального времени можно выразить так: система жесткого реального времени никогда не опаздывает с реакцией на событие, система мягкого реального времени - не должна опаздывать с реакцией на событие.

## СТРУКТУРА СРВ

Любая система реального масштаба времени может быть описана как состоящая из трех основных подсистем.

**Управляемая (контролируемая) подсистема** (например, индустриальный завод, управляемое компьютером транспортное средство), диктует требования в реальном масштабе времени; **подсистема контроля (контролирующая)** управляет некоторыми вычислениями и связью с оборудованием для использования от управляемой подсистемы; **подсистема оператора (операционная)** контролирует полную деятельность системы.

Интерфейс между управляемыми и подсистемами контроля состоит из таких устройств как датчики и приводы. Интерфейс между управляющей подсистемой и оператором связывает человека с машинной.

Управляемая подсистема представлена задачами (в дальнейшем называемыми прикладными задачами) которые используют оборудование, управляемое подсистемой контроля. Эта последняя подсистема может быть построена из очень большого количества процессоров, управляющими такими местными ресурсами, как память и устройства хранения, и доступ к локальной сети в реальном масштабе времени. Эти процессоры и ресурсы управляются системой программного обеспечения, которую мы называем **операционной системой реального масштаба времени** (RTOS – real time operating system).

## ОСРВ и ОС общего назначения

Назовем **операционной системой реального времени** такую систему, которая может быть использована для построения систем жесткого реального времени.

Это определение выражает отношение к операционным системам реального времени как к объекту, содержащему необходимые инструменты, но также означает, что этими инструментами еще необходимо правильно воспользоваться.

Большинство программного обеспечения ориентировано на «слабое» реальное время, а задача СРВ – обеспечить уровень безопасного функционирования системы, даже если управляющая программа никогда не закончит своей работы.

ОС общего назначения, особенно многопользовательские, такие как UNIX, ориентированы на оптимальное распределение ресурсов компьютера между пользователями и задачами (системы разделения времени), В операционных системах реального времени подобная задача отходит на второй план - все отступает перед главной задачей - успеть среагировать на события, происходящие на объекте.

Другое отличие - применение операционной системы реального времени всегда связано с аппаратурой, с объектом, с событиями, происходящими на объекте. Система реального времени, как аппаратно-программный комплекс, включает в себя датчики, регистрирующие события на объекте, модули ввода-вывода, преобразующие показания датчиков в цифровой вид, пригодный для обработки этих показаний на компьютере, и, наконец, компьютер с программой, реагирующей на события, происходящие на объекте. Операционная система реального времени ориентирована на обработку внешних событий. Именно это приводит к коренным отличиям (по сравнению с ОС общего назначения) в структуре системы, в функциях ядра, в построении системы ввода-вывода.

Операционная система реального времени может быть похожа по пользовательскому интерфейсу на ОС общего назначения (к этому, кстати, стремятся почти все производители операционных системах реального времени), однако устроена она совершенно иначе - об этом речь впереди. Кроме того, применение операционных системах реального времени всегда конкретно. Если ОС общего назначения обычно воспринимается пользователями (не разработчиками) как уже готовый набор приложений, то операционная система реального времени служит только инструментом для создания конкретного аппаратно-программного комплекса реального времени. И поэтому наиболее широкий класс пользователей операционных системах реального времени - разработчики комплексов реального времени, люди, проектирующие системы управления и сбора данных. Проектируя и разрабатывая конкретную систему реального времени, программист всегда точно знает, какие события могут произойти на объекте, знает критические сроки обслуживания каждого из этих событий. Одно из коренных внешних отличий систем реального времени от систем общего назначения - четкое разграничение систем разработки и систем исполнения.

**Система исполнения** операционных системах реального времени - набор инструментов (ядро, драйверы, исполняемые модули), обеспечивающих функционирование приложения реального времени. Большинство современных ведущих операционных систем реального времени поддерживают целый спектр аппаратных архитектур, на которых работают системы исполнения (Intel, Motorola, RISC, MIPS, PowerPC, и другие). Это объясняется тем, что набор аппаратных средств - часть комплекса реального времени и аппаратура должна быть также адекватна решаемой задаче, поэтому ведущие операционные системы реального времени перекрывают целый ряд наиболее популярных архитектур, чтобы удовлетворить самим разным требованиям по части аппаратуры.

Система исполнения операционных системах реального времени и компьютер, на котором она исполняется называют "**целевой**" (target) системой. Система разработки - набор средств, обеспечивающих создание и отладку приложения реального времени.

**Системы разработки** (компиляторы, отладчики и всевозможные tools) работают, как правило, в популярных и распространенных ОС, таких, как UNIX и Windows. Кроме того, многие операционные системы реального времени имеют и так называемые резидентные средства разработки, исполняющиеся в среде самой операционной системы реального времени. Заметим, что функционально средства разработки операционных систем реального времени отличаются от привычных систем разработки, таких, например, как Developers Studio, TaskBuilder, так как часто они содержат средства удаленной отладки, средства профилирования (измерение времен выполнения отдельных участков кода), средства эмуляции целевого процессора, специальные средства отладки взаимодействующих задач, а иногда и средства моделирования.

## ХАРАКТЕРИСТИКИ ОСРВ

Как было сказано ранее, сердцем системы реального времени является ОСРВ (операционная система реального времени). В связи со специфичностью решаемых задач, ОСРВ должна обладать определенными свойствами.

**Время реакции системы на внешние события.** Согласно определению, ОСРВ должна обеспечить требуемый уровень сервиса в заданный промежуток времени. Этот промежуток времени задается обычно периодичностью и скоростью процессов, которым управляет система.

Приблизительное время реакции в зависимости от области применения ОСРВ может быть следующее:

- математическое моделирование - несколько **микросекунд**

- радиолокация - несколько **миллисекунд**

- складской учет - несколько **секунд**

- управление производством - несколько **минут**

Видно, что времена очень разнятся и накладывают различные требования на вычислительную установку, на которой работает ОСРВ.

Итак, как же определить время реакции системы? Поймем, какие времена мы должны знать для того, чтобы предсказать время реакции системы. События, происходящие на объекте, регистрируются датчиками, данные с датчиков передаются в модули ввода-вывода (интерфейсы) системы. Модули ввода-вывода, получив информацию от датчиков и преобразовав ее, генерируют запрос на прерывание в управляющем компьютере, подавая ему тем самым сигнал о том, что на объекте произошло событие. Получив сигнал от модуля ввода-вывода, система должна запустить программу обработки этого события. Интервал времени - от события на объекте и до выполнения первой инструкции в программе обработки этого события и является **временем реакции системы на события**, и, проектируя систему реального времени, разработчики должны уметь вычислять этот интервал. Из чего он складывается? Время выполнения цепочки действий - от события на объекте до генерации прерывания - никак не зависит от операционных систем реального времени и целиком определяется аппаратурой, а вот интервал времени - от возникновения запроса на прерывание и до выполнения первой инструкции обработчика определяется целиком свойствами операционной системы и архитектурой компьютера. Причем это время нужно уметь оценивать в худшей для системы ситуации, то есть в предположении, что процессор загружен, что в это время могут происходить другие прерывания, что система может выполнять какие-то действия, блокирующие прерывания. В ОСРВ заложен параллелизм, возможность одновременной обработки нескольких событий, поэтому все операционные системы реального времени являются многозадачными (многопроцессными, многонитевыми). Для того, чтобы уметь оценивать накладные расходы системы при обработке параллельных событий, необходимо знать время, которое система затрачивает на передачу управления от процесса к процессу (от задачи к задаче, от нити к нити), то есть **время переключения контекста**.

ОСРВ содержат механизмы, гарантирующие заранее вычисленное время реакции системы.

Эта гарантия достигается знанием максимального времени блокировок прерываний в системе, времени переключения контекста, времен выполнения различных системных вызовов, применением нужных механизмов диспетчеризации и пр. Т.е. время реакции на события для операционных систем реального времени можно вычислить с большой точностью. Эти вычисления невозможны для операционных систем LINUX и Windows NT - здесь можно полагаться только на результаты тестирования, эмпирические оценки. Часто производительность компьютера подбирается таким образом, чтобы успевать в нужные времена, но сути дела это не меняет, поэтому риски в сложных комплексах могут оказаться велики - при небольшом изменении внешних условий или при модификации приложений времена могут "поплыть". Что касается расширений реального времени для LINUX и Windows NT, то здесь, по крайней мере, можно полагаться на времена, полученные при тестировании.

**Время перезагрузки системы.** Этот параметр кажется второстепенным, однако были свидетелями случаи, когда именно этот параметр целиком определял выбор дорогой операционной системы (время перезагрузки не должно было превышать 1 секунду). Этот параметр важен для систем, от которых требуется непрерывная работа; в этих случаях ставятся ловушки, отслеживающие зависание системы или приложений, и, если таковое произошло, автоматически перезагружающие систему (такие ловушки необходимы в системах повышенной надежности, т.к. от ошибок, по крайней мере, в приложениях никто не застрахован). В таких случаях важным является такое свойство системы как ее живучесть при незапланированных перезагрузках. Большинство операционных систем реального времени устойчивы к перезагрузкам и могут быть прерваны и перезагружены в любое время.

Время загрузки для разных ОСРВ колеблется от секунды до нескольких десятков секунд. В большинстве систем (OS9, VxWorks) время загрузки можно регулировать, изменяя стартовые последовательности. В ОС LINUX время загрузки в стандартном варианте более минуты, система неустойчива к внезапным остановам - требуется стандартная процедура завершения работы с системой (shutdown). Однако LINUX достаточно гибок и можно создать конфигурации системы, в которых время загрузки будет уменьшено до десятка секунд и система будет устойчива к сбоям (использование специальной опции файловой системы). В Windows NT время загрузки более минуты, система неустойчива к внезапным сбоям. Использование расширений реального времени (RTX) позволяет детектировать зависания системы и выполнить в этих случаях необходимые операции по спасению данных и по выполнению каких-то страховочных действий.

Посмотрим, какие ОС могут использоваться в системах реального времени в зависимости от времени реакции системы.

Вычислительные установки, на которых применяются ОСРВ, можно разделить на три группы:

- **«Обычные» компьютеры.** По логическому устройству совпадают с настольными системами. Аппаратное устройство несколько отличается. Для обеспечения минимального времени простоя в случае технической неполадки процессор, память и т.д. размещаются на съемной плате, вставляемой в специальный разъем так называемой «пассивной» основной платы. В другие разъемы этой платы

вставляются платы периферийных устройств. Среди процессоров таких компьютеров преобладают процессоры Intel.

- **Промышленные компьютеры.** Состоят из одной платы, на которой размещены процессор, контроллер памяти, память. Память может быть нескольких видов – ПЗУ (в которой размещается сама ОСРВ), ОЗУ (там размещаются код и данные), Флеш-память (может играть роль диска). На плате также находятся контроллеры периферийных устройств, несколько программируемых таймеров. Среди процессоров этих компьютеров доминируют процессоры семейства PowerPC, Motorola 68xxx, SPARC, ARM, Intel 80x86, 80960x.

- **Встраиваемые системы.** Устанавливаются внутрь оборудования, которым они управляют. Для крупного оборудования могут по исполнению совпадать с промышленными компьютерами. Для оборудования поменьше могут представлять собой процессор с сопутствующими элементами, размещенными на одной плате с другими электронными компонентами оборудования. Для миниатюрных систем процессор с сопутствующими элементами может быть частью одной из интегральных схем оборудования.

В связи с особенностями оборудования ОСРВ (промышленные компьютеры и встраиваемые системы часто являются бездисковыми.) должны обладать следующими свойствами:

**Размеры системы.** Для систем реального времени важным параметром является размер системы исполнения, а именно суммарный размер минимально необходимого для работы приложения системного набора (ядро, системные модули, драйверы и т. д.). Хотя, надо признать, что с течением времени значение этого параметра уменьшается, тем не менее он остается важным и производители систем реального времени стремятся к тому, чтобы размеры ядра и обслуживающих модулей системы были невелики.

Примеры: размер ядра операционной системы реального времени OS-9 на микропроцессорах Motorola 68xxx - 22 KB, VxWorks - 16 KB.

**Возможность исполнения системы из ПЗУ (ROM).** Система должна иметь возможность осуществлять загрузку из ПЗУ. Для экономии места в ПЗУ часть системы может храниться в сжатом виде и загружаться в ОЗУ по мере необходимости. Часто система позволяет исполнять код как в ПЗУ, так и в ОЗУ. При наличии свободного места в ОЗУ система может копировать себя из медленного ПЗУ в более быстрое ОЗУ.

К дополнительным свойствам ОСРВ можно отнести следующие:

**Наличие необходимых драйверов устройств.** Если разрабатываемая система имеет обширную периферию, то наличие уже готовых драйверов может оказать большое влияние на выбор операционной системы. Естественно, самый большой набор драйверов создан для операционных системах LINUX и Windows NT. Наиболее популярные операционные системы реального времени, такие как VxWorks, OS9, QNX, также имеют обширные наборы готовых драйверов и, кроме того, содержат средства для их быстрой разработки.

**Поддержка процессоров различной архитектуры.** В связи с тем, что в промышленных компьютерах, серверах, встраиваемых системах широко распространены процессоры разной архитектуры с различной системой команд, ОСРВ по возможности должна поддерживать как можно более широкий ряд процессоров.

Одной из важных характеристик ОСРВ является наличие **специального кроссплатформенного инструментария разработчика**. Это связано с тем, что разработка СРВ часто проводится на «обычном» компьютере, отличном по архитектуре от компьютера, на котором будет устанавливаться СРВ. При этом ОС на этих двух компьютерах также может не совпадать.

## МЕХАНИЗМЫ РЕАЛЬНОГО ВРЕМЕНИ

Важнейшими характеристиками ОСРВ являются заложенные в операционную систему **механизмы реального времени**.

Процесс проектирования конкретной системы реального времени начинается с тщательного изучения объекта. Разработчики проекта исследуют объект, изучают возможные события на нем, определяют критические сроки реакции системы на каждое событие и разрабатывают алгоритмы обработки этих событий. Затем следует процесс проектирования и разработки программных приложений. Какие же механизмы в операционных системах реального времени делают систему реального времени (СРВ) предсказуемой?

*Система приоритетов и алгоритмы диспетчеризации.* Базовыми инструментами разработки сценария работы системы являются система приоритетов процессов (задач) и алгоритмы планирования (диспетчеризации) операционных системах реального времени.

В многозадачных ОС общего назначения используются, как правило, различные модификации алгоритма круговой диспетчеризации, основанные на понятии непрерывного кванта времени ("time slice"), предоставляемого процессу для работы. Планировщик по истечении каждого кванта времени просматривает очередь активных процессов и принимает решение, кому передать управление, основываясь на приоритетах процессов (численных значениях, им присвоенных).

Приоритеты могут быть фиксированными или меняться со временем - это зависит от алгоритмов планирования в данной ОС, но рано или поздно процессорное время получат все процессы в системе.

Алгоритмы круговой диспетчеризации неприменимы в чистом виде в операционных системах реального времени. Основной недостаток - непрерывный квант времени, в течение которого процессором владеет только один процесс. Планировщики же операционных систем реального времени имеют возможность сменить процесс до истечения "time slice", если в этом возникла необходимость. Один из возможных алгоритмов планирования при этом "приоритетный с вытеснением". Мир операционных систем реального времени отличается богатством различных алгоритмов планирования: динамические, приоритетные, монотонные, адаптивные и пр., цель же всегда преследуется одна - предоставить инструмент, позволяющий в нужный момент времени исполнять именно тот процесс, который необходим.

*Механизмы межзадачного взаимодействия.* Другой набор механизмов реального времени относится к средствам синхронизации процессов и передачи данных между ними. Для операционных систем реального времени характерна развитость этих механизмов. К таким механизмам относятся: семафоры, мьютексы, события, сигналы, средства для работы с разделяемой памятью, каналы данных (pipes), очереди сообщений. Многие из подобных механизмов используются и в ОС общего назначения, но их реализация в

операционных системах реального времени имеет свои особенности - время исполнения системных вызовов почти не зависит от состояния системы, и в каждой операционной системе реального времени есть по крайней мере один быстрый механизм передачи данных от процесса к процессу.

*Средства для работы с таймерами.* Такие инструменты, как средства работы с таймерами, необходимы для систем с жестким временным регламентом, поэтому развитость средств работы с таймерами - необходимый атрибут операционных систем реального времени. Эти средства, как правило, позволяют:

- измерять и задавать различные промежутки времени (от 1 мкс и выше),

- генерировать прерывания по истечении временных интервалов,

- создавать разовые и циклические будильники

Здесь описаны только базовые, обязательные механизмы, использующиеся в ОСРВ. Кроме того, почти в каждой операционной системе реального времени имеется целый набор дополнительных, специфических только для нее механизмов, касающийся системы ввода-вывода, управления прерываниями, работы с памятью. Каждая система содержит также ряд средств, обеспечивающих ее надежность. Позже механизмы реального времени будут рассмотрены подробнее.

## ЧАСЫ И ТАЙМЕРЫ

В ОСРВ используются различные службы времени. Операционная система отслеживает текущее время, в определенное время запускает задачи и потоки и приостанавливает их на определенные интервалы. В службах времени ОСРВ используются часы реального времени. Обычно используются высокоточные аппаратные часы. Для отсчета временных интервалов на основе часов реального времени создаются таймеры. Для каждого процесса и потока определяются часы процессорного времени. На базе этих часов создаются таймеры; которые измеряют перерасход времени процессом или потоком, позволяя динамически выявлять программные ошибки или ошибки вычисления максимально возможного времени выполнения. В высоконадежных, критичных ко времени системах важно выявление ситуаций, при которых задача превышает максимально возможное время своего выполнения, т.к. при этом работа системы может выйти за рамки допустимого времени отклика. Часы времени выполнения позволяют выявить возникновение перерасхода времени и активизировать соответствующие действия по обработке ошибок. Большинство ОСРВ оперируют относительным временем. Что-то происходит "до" и "после" некоторого другого события. В системе, полностью управляемой событиями, необходим часовой механизм (ticker), т.к. там нет квантования времени (time slicing). Однако, если нужны временные метки для некоторых событий или необходим системный вызов типа "ждать одну секунду", то нужен тактовый генератор и/или таймер. Синхронизация в ОСРВ осуществляется с помощью механизма блокирования (или ожидания) до наступления некоторого события. Абсолютное время не используется. Реализации в ОСРВ других концептуальных абстракций подобны их реализациям в традиционных ОС.

# ГЛАВА-II. КОНТРОЛЬ И УПРАВЛЕНИЯ В СИСТЕМАХ РЕАЛЬНОГО ВРЕМЕНИ

## ЛЕКЦИЯ 2.1. ЗАДАЧИ КОНТРОЛЯ И УПРАВЛЕНИЯ, ТИПЫ ОБЪЕКТОВ, ОБРАБОТКА И ПОРЯДОК РАБОТЫ УПРАВЛЕНИЯ СИСТЕМ РЕАЛЬНОГО ВРЕМЕНИ.

---

### План

- Управление как процесс принятия и реализации решений

- Классификация систем управления

- Структура систем реального времени

Под системой принято понимать совокупность связанных между собой элементов. Система характеризуется структурой  $S = \langle E, C, \lambda \rangle$ , где  $E$  – множество элементов,  $C$  – множество связей между элементами,  $\lambda$  – соответствие между элементами. При этом элементом называется часть системы, не подлежащая дальнейшему делению на части при данном уровне рассмотрения. Элементы могут представлять собой понятия, и тогда мы будем иметь дело с понятийной системой; если элементами системы являются физические объекты, то налицо техническая система. Заметим, что в определении отмечается некоторая совокупность, т.е. некоторая целостность. Нас интересуют не отдельные элементы, а все вместе, взятые в некотором единстве. Принципиальным является необходимость учета взаимодействия элементов, так как именно оно придает совокупности элементов новое качество. Часть элементов системы, выделенная на основе какой-либо общности элементов, называется подсистемой. Системы, создаваемые человеком, обладают целью функционирования. Именно наличие цели служит тем объединяющим фактором, на основе которого объединяются элементы. Такие системы называют организованными системами.

### УПРАВЛЕНИЕ КАК ПРОЦЕСС ПРИНЯТИЯ И РЕАЛИЗАЦИИ РЕШЕНИЙ

В повседневной деятельности мы часто сталкиваемся с терминами «управлять», «регулировать» и понимаем под этими терминами задачу воздействия на параметры объекта для достижения определенных целей. Естественно называть управлением целенаправленное изменение параметров объекта управления. Совокупность наиболее важных параметров, от которых зависит функционирование объекта управления, описывает его состояние. Знание состояния объекта управления – важнейший фактор, определяющий принятие решения по управлению. Другой важный фактор – возмущения, которым подвергается объект управления со стороны других объектов, состоянием которых мы не можем управлять. Множество таких объектов объединяется понятием «внешняя среда». На основе оценок состояния объекта управления и внешней среды принимается решение по управлению. Конечно, при этом учитывается цель функционирования и ресурсы, которыми мы располагаем. После того, как решение принято, оно реализуется с потреблением ресурсов. Так мы приходим к структурной схеме процесса управления.

Управление осуществляется путем выдачи на объект управляющих воздействий

$$X(t) = (x_1, x_2, \dots, x_n; t).$$

Кроме них, объект управления подвергается воздействию возмущений со стороны внешней среды; часть из них

$$Z(t) = (z_1, z_2, \dots, z_m; t)$$

измеряется, другая часть

$$F(t) = (f_1, f_2, \dots, f_s; t)$$

неизвестна (часто неизвестно также значение  $s$ ). Контролируемые параметры, по которым ведется управление,

$$Y(t) = (y_1, y_2, \dots, y_r; t),$$

называются управляемыми. Управляемые параметры дают обобщенную информацию о состоянии объекта управления

$$S(t) = (s_1, s_2, \dots, s_k; t).$$

Смена состояний объекта управления определяет процесс его функционирования:

$$S(t) = \phi[X(t), Z(t), F(t), Y(t), S(t-1)].$$

Задача управления состоит в том, чтобы найти такую функцию  $X(t)$ , которая обеспечила бы перевод объекта в заданное конечное состояние  $S^*$ , соответствующее цели его функционирования. Этот перевод должен закончиться за конечное число шагов и требовать минимальных затрат ресурсов  $R$ .

## КЛАССИФИКАЦИЯ СИСТЕМ УПРАВЛЕНИЯ

Тип системы зависит от того, как принимается решение по управлению. Если в процессе принятия решения участвует человек, то такая система называется автоматизированной (АСУ); если человек исключен из процесса принятия решения, то это – автоматическая система управления (САУ). По физической природе объекта управления различают системы управления технологическими процессами, где объект управления представляет собой физический объект, и системы управления экономико-организационного типа, в которых объектом управления является хозяйственная деятельность. В последнее время создаются интегрированные системы управления, в которых присутствуют объекты обоих типов. Другим признаком, по которому классифицируются системы, является время принятия решения. В системах управления оно зависит от динамики объекта, которая может быть различной: от миллисекунд до часов и дней. Условная граница лежит на уровне 100 мс: если время принятия решения не превышает этой величины, то говорят, что система функционирует в реальном масштабе времени; если превышает, то говорят о произвольном масштабе. Системы управления технологическими процессами всегда функционируют в реальном масштабе времени. Время в таких системах является одним из факторов, определяющих эффективность системы.

Хорошим примером системы реального времени является промышленный робот, который должен брать что-то с ленты конвейера. Объекты на конвейере движутся, и робот имеет некоторый интервал времени для того, чтобы схватить объект. Если робот опоздает, то объекта уже не будет на месте и поэтому работа будет неверной. Если робот поспешит, то объекта там еще не будет. Принято различать системы «жесткого» и «мягкого» реального времени. Системой «жесткого» реального времени называют систему, в которой

неспособность обеспечить реакцию на какие-либо события в заданное время является отказом и ведет к невозможности решения поставленной задачи. В качестве условной временной границы допустимого времени реакции обычно принимают 100 мкс. В жесткой системе: - никакое опоздание неприемлемо ни при каких обстоятельствах; - результат, выданный с опозданием, бесполезен; - нарушение крайнего срока времени отклика рассматривается как катастрофический отказ; - цена превышения заданного времени отклика бесконечно велика. Точного определения для «мягкого» реального времени не существует, но принято считать, что она иногда может не успевать делать все, что надо, в установленные сроки. В мягкой системе: - возрастает цена за опоздание результата; - критическим фактором является низкая производительность, а не опоздания.

В терминах вероятностей эти определения могут быть записаны следующим образом:

$$P\{|t - t_0| > \Delta t\} > 0$$

– для систем «мягкого» реального времени,

$$P\{|t - t_0| > \Delta t\} = 0$$

– для систем «жесткого» реального времени (здесь  $t$  – фактический момент выдачи управляющего воздействия,  $t_0$  – заданный момент выдачи управляющего воздействия,  $\Delta t$  – допустимая погрешность).

В зависимости от функций, выполняемых системой управления, различают виды (формы) автоматизации: управление, регулирование, контроль, защиту и блокировку.

**Управление** представляет собой принятие решений и выдачу на объект управления совокупности воздействий, выполняемых на основании информации о ходе технологического процесса, с целью поддержания требуемого технологического режима или улучшения его параметров. Обычно предполагается, что управление подразумевает поиск и реализацию оптимального (по определенному критерию) решения.

**Регулирование** представляет собой принятие решений и выдачу на объект управления совокупности воздействий, выполняемых на основании информации о ходе технологического процесса, с целью поддержания параметров производственных процессов постоянными или изменяющимися по заданному закону.

**Контроль** – это наблюдение за параметрами объекта управления с целью определения его состояния. Параметры, подлежащие контролю, в зависимости от их физической природы различны (температура, давление, расход топлива, число оборотов, сила тока и т.п.). Контроль может быть местным и дистанционным. Местный контроль дает возможность наблюдать за состоянием параметра непосредственно в контролируемой точке. При дистанционном контроле за состоянием параметров можно следить на расстоянии от контролируемой точки.

**Защита** – это комплекс средств и мероприятий по предохранению агрегатов и установок при нарушениях технологических режимов.

**Блокировка** – это комплекс средств и мероприятий, предохраняющих участок установки или агрегат от неправильных операций вследствие невнимательности оператора или ошибочных команд. Различают две группы блокировки: запретно-разрешающую и аварийную.

*Запретно-разрешающие блокировки* предотвращают неправильные включения и отключения механизмов, а также нарушение установленной технологическими требованиями очередности пуска и остановки различных механизмов.

*Аварийные блокировки* предназначены для автоматического последовательного отключения (включения) механизмов в соответствии с режимом работы агрегата, подвергшегося аварийному отключению. Блокировочные устройства применяют также в случаях, когда требуется исключить одновременную подачу команд противоположного знака на один и тот же регулирующий орган из разных мест или от автоматического и дистанционного управления, когда оба вида управления действуют параллельно.

## СТРУКТУРА СИСТЕМ РЕАЛЬНОГО ВРЕМЕНИ

Основными составляющими автоматизированных систем реального времени (АСУ ВР) являются комплекс технических средств, программное и информационное обеспечение. Для принятия решения по управлению нужно знать о состоянии объекта управления и возмущениях со стороны внешней среды. Эта информация вводится в систему с помощью измерительных средств, которые являются источниками информации для средств переработки информации. Эти средства реализуют алгоритм принятия решения и формируют управляющие воздействия, которые передаются на исполнительные средства, непосредственно связанные с изменяемыми параметрами объекта управления. Для того чтобы человек участвовал в процессе принятия решения, ему также нужно дать возможность следить за состоянием объекта и внешней среды. Для этого он снабжается устройствами отображения информации, которые предназначены для преобразования информации в удобную для восприятия форму (чаще всего – в визуальную). Человек может вмешиваться в управление, воздействуя на исполнительные средства и на средства переработки информации с помощью управляющих средств. Поскольку части системы могут находиться на значительных расстояниях друг от друга, часть связей представляет собой средства передачи данных – специальные технические устройства, предназначенные для этих целей. Еще одна составляющая комплекса технических средств – система энергоснабжения; ее назначение – снабжение всех технических средств электроэнергией заданного напряжения и мощности.

В качестве средств переработки информации обычно применяется узел на основе вычислительной машины. Тип и структура этого узла может быть различной – от простейшего контроллера до кластера, однако в любом случае его применение связано со следующими особенностями: – он должен «следить» за множеством параллельно протекающих процессов; – он должен обрабатывать запросы, поступающие в произвольные моменты времени; – допустимое время принятия решения обычно соизмеримо с временем реализации алгоритма выработки такого решения; – он должен удовлетворять повышенным требованиям по надежности и достоверности информации; – состав задач, которые решает этот узел, заранее известен и программное обеспечение для их решения отлажено. Эти особенности учитываются при построении программного обеспечения. Оно включает в себя операционную систему, программы решения функциональных задач и программы контроля и обеспечения устойчивости вычислительного процесса.

Главное назначение операционной системы – обеспечение параллелизма и обработка заявок, поступающих в случайные моменты времени. Программы решения

функциональных задач выполняют основное целевое назначение системы – управление объектом. Третья группа программ контролирует работу системы. Информационное обеспечение содержит данные, необходимые для управления системой.

# ГЛАВА-III. СРЕДСТВА ПЕРЕРАБОТКИ ИНФОРМАЦИИ

## ЛЕКЦИЯ 3.1. КЛАССИФИКАЦИЯ ВЫЧИСЛИТЕЛЬНЫХ СИСТЕМ. Многомашинные вычислительные системы

---

### План

- Классификация ВС

- Многомашинные вычислительные системы

- Уровни комплексирования

Первые вычислительные системы включали большие и дорогие ЭВМ, в связи с чем их количество в такой системе не превышало трех – четырех. Появление персональных компьютеров привело к построению распределенных систем управления, в которые могут быть вовлечены десятки и сотни компьютеров – персональных рабочих станций.

Эффективность использования вычислительных систем во многом определяется возможностями организации параллельных вычислений на уровне алгоритмов и программ. Когда параллелизм реализуется внутри процессора (с помощью, например, конвейерного АЛУ или нескольких АЛУ), то такая вычислительная структура определяется как *векторный* или *суперскалярный* процессор.

Если параллелизм обеспечивается путем объединения нескольких ЭВМ или процессоров, то такая вычислительная структура определяется как *вычислительная система*.

Вычислительная система, в которой отдельные ЭВМ или процессоры объединяются вместе посредством специального коммуникационного оборудования (каналов связи), представляет собой *вычислительную сеть*.

Отличительной особенностью вычислительной системы по отношению к ЭВМ является наличие в них нескольких вычислителей(процессоров или ЭВМ), реализующих параллельную обработку. Создание ВС преследует следующие основные цели: повышение производительности системы за счет ускорения процессов обработки данных, повышение надежности и достоверности вычислений, предоставление пользователям дополнительных сервисных услуг и т.д.

В системах управления реального времени используются специализированные вычислительные системы, ориентированные на решение узкого класса задач. Специализация ВС может обеспечиваться различными средствами:

- во-первых, сама структура системы (количество параллельно работающих элементов, связи между ними и т.д.) может быть ориентирована на определенные виды обработки информации: матричные вычисления, решение алгебраических, дифференциальных и интегральных уравнений и т.п. Практика разработки таких ВС показала, что, чем уже класс задач, для решения которых предназначается специализированная ВС, тем большую производительность можно обеспечить;

- во-вторых, специализация ВС может закладываться включением в их состав специального оборудования и специального программного обеспечения.

Специализированные ВС по *виду составляющих элементов* принято подразделять на *многомашинные* и *многопроцессорные*.

*Многомашинная ВС (MMC) содержит несколько ЭВМ, каждая из которых имеет свою оперативную память и работает под управлением своей операционной системы. Обмен между ЭВМ идет с помощью специальных дополнительных программных и аппаратурных средств. Многомашинные ВС относятся к классу систем с распределенной памятью.*

*Многопроцессорная (мультипроцессорная) система (МПС) в качестве общего ресурса имеет общую оперативную память (ООП).*

Все процессоры работают с единым адресным пространством. Параллельная работа процессоров и использование ООП обеспечивается единой операционной системой. Все процессоры «разделяют» общую память, поэтому многопроцессорные ВС относятся к классу систем с разделяемой памятью.

По **типам ЭВМ или процессоров**, из которых состоит ВС, различают однородные и неоднородные системы. Однородные системы мы предполагают комплексирование однотипных ЭВМ (процессоров), неоднородные – разнотипных. В однородных системах значительно упрощается разработка и обслуживание технических и программных средств. В них обеспечивается возможность стандартизации и унификации соединений и процедур взаимодействия элементов системы. Упрощается обслуживание систем, облегчается модернизация и их развитие. Вместе с тем существуют и неоднородные ВС, в которых комплексируемые элементы очень сильно отличаются по своим техническим и функциональным характеристикам и могут представлять собой специализированные процессоры.

По **характеру пространственного распределения** вычислительных модулей ВС делятся на системы сосредоточенного (локального) и распределенного типов. Обычно такое деление касается только MMC.

В локальных и распределенных MMC сильно различается оперативность взаимодействия в зависимости от удаленности ЭВМ. Время передачи информации между соседними ЭВМ, соединенными простым кабелем, может быть много меньше времени передачи данных по каналам связи. Как правило, все выпускаемые в мире ЭВМ имеют средства прямого взаимодействия и средства подключения к сетям ЭВМ.

По **методам управления элементами ВС** различают централизованные, децентрализованные и со смешанным управлением. Помимо параллельных вычислений, производимых элементами системы, необходимо выделять ресурсы на обеспечение управления этими вычислениями. В централизованных ВС за это отвечает главная, или диспетчерская, ЭВМ (процессор). Ее задачей является распределение нагрузки между элементами, выделение ресурсов, контроль состояния ресурсов, координация взаимодействия. Структура ВС может быть одноуровневой или иерархической. Централизованный орган управления в системе может быть жестко фиксирован, или эти функции могут передаваться другой ЭВМ (процессору), что способствует повышению надежности системы. Централизованные системы имеют более простые операционные системы (ОС). В децентрализованных системах функции управления распределены между ее элементами. Каждая ЭВМ (процессор) системы сохраняет известную автономию, а необходимое взаимодействие между элементами устанавливается по специальным наборам сигналов. С развитием ВС и, в частности, сетей ЭВМ интерес к децентрализованным системам постоянно растет.

В системах со смешанным управлением совмещаются процедуры централизованного и децентрализованного управления. Перераспределение функций осуществляется в ходе вычислительного процесса, исходя из сложившейся ситуации.

По **принципу закрепления вычислительных функций** за отдельными ЭВМ (процессорами) различают системы с *жестким* и *плавающим закреплением функций*. В зависимости от типа ВС следует решать задачи статического или динамического размещения программных модулей и массивов данных, обеспечивая необходимую гибкость системы и надежность ее функционирования.

### ***Многомашинные вычислительные системы***

Исторически многомашинные вычислительные системы появились первыми. Уже при использовании ЭВМ первых поколений возникали задачи повышения производительности, надежности и достоверности вычислений.

Многомашинный комплекс состоит из нескольких ЭВМ, каждая из которых имеет свою внутреннюю память и работает под управлением своей операционной системы, и средства обмена информацией между машинами. В отличие от них мультипроцессорные ВС имеют общую память и общие периферийные устройства; они работают под управлением единой операционной системы.

Машины работают параллельно; каждая из них обрабатывают собственные потоки задач, а в системах управления решает собственное подмножество функциональных задач. Несколько ЭВМ только тогда представляют собой вычислительную систему, когда они могут обмениваться информацией. Для этого требуется их совместимость.

*Аппаратурная совместимость* означает, что:

- подключаемые друг к другу элементы (узлы, блоки) должны иметь единые стандартные, унифицированные средства соединения: кабели, число проводов в них, единое назначение проводов, разъемы, заглушки, адаптеры, платы и т.д.;

- параметры электрических сигналов, которыми обмениваются элементы (узлы, устройства), тоже должны соответствовать друг другу: амплитуды импульсов, полярность, длительность и т.д.;

- должна быть решена проблема синхронизации вычислений;

- должна быть согласована форма представления чисел и их разрядность.

*Программная совместимость* предполагает, что:

- существует программа-диспетчер, которая оперативно распределяет ресурсы ВС между задачами, обеспечивает загрузку программ и управляет вводом-выводом;

- программы, которыми могут обмениваться ЭВМ, входящие в

- состав ВС, должны одинаково интерпретироваться ими (должна быть согласована адресация, разрядности кодов команд коды операций и др.).

Эта проблема решается достаточно просто для однотипных ЭВМ.

Программная совместимость может обеспечиваться на уровнях:

1. внутреннего языка;

2. языка ассемблера;

3. языка высокого уровня.

На первом уровне наиболее распространены такие типы организации совместимости, как «общая наименьшая машина», иерархического типа, частичная и с эмуляцией недостающих команд.

Если на ЭВМ1 можно выполнять множество команд А, а на ЭВМ2 – множество команд В и пересечение этих множеств С не пусто, то оно соответствует возможностям «общей наименьшей машины».

Если одно множество полностью входит в другое, то имеет место иерархическая совместимость. Например, если взаимодействующие ЭВМ относятся к одному и тому же семейству, но стыкуются разные модели, то в таких моделях совместимость обеспечивается «снизу вверх», т.е. ранее созданные программы могут выполняться на более поздних моделях, но не наоборот.

Частичная совместимость возникает тогда, когда только часть программ, составленных для одной ЭВМ, может выполняться на другой. Эмуляция отсутствующих команд служит для увеличения степени частичной совместимости: если выполнение программы на малой ЭВМ прерывается из-за отсутствия в ней команд, существующих в большой ЭВМ, то эти команды могут эмулироваться программными средствами малой ЭВМ.

Совместимость на уровне машинных команд имеет следующие недостатки:

- разработка и отладка программ для обеспечения совместимости на этом уровне требует больших затрат времени и сил, особенно, для управляющих ЭВМ;

- эта совместимость приводит к неполному использованию специального оборудования и специальных команд, которые имеются не во всех ЭВМ;

- для надежного обмена программами требуется централизация их контроля и исправления ошибок.

Наиболее высокая степень программной совместимости – на третьем уровне – уровне алгоритмических языков, когда обмен программами, по существу, заменяется обменом алгоритмами. Совместимость на втором уровне имеет промежуточный характер.

*Информационная* совместимость предполагает, что передаваемые информационные массивы одинаково интерпретируются стыкуемыми модулями ВС. Должны быть стандартизированы алфавиты, разрядность, форматы, структура и разметка файлов, томов и т.д.

Эффективность ММС во многом зависит от организации обмена информацией и командами между ними. Характеристики обмена определяются параметрами технических средств, обеспечивающих взаимодействие устройств, и уровня управления процессами, на котором это взаимодействие осуществляется. В общем случае возможны следующие уровни комплексирования:

- прямого управления (процессор – процессор);

- общей оперативной памяти;

- комплексируемых каналов ввода-вывода;

- устройств управления внешними устройствами;

- общих внешних устройств.

Чаще всего комплексирование ЭВМ в ММС осуществляется на первом, втором и третьем уровнях.

**Уровень прямого управления** служит для передачи коротких приказов-сообщений. Последовательность взаимодействия процессоров сводится к следующему. Процессор ЭВМ-инициатора обмена передает в блок прямого управления сообщение и подает команду «Прямая запись». У процессора другой ЭВМ эта команда вызывает прерывание, относящееся к классу внешних. В ответ он вырабатывает команду «Прямое чтение» и записывает передаваемый байт в свою память. Затем принятая информация

расшифровывается и по ней принимается решение. После завершения передачи прерывания снимаются, и оба процессора продолжают вычисления по собственным программам. Очевидно, что уровень прямого управления не может использоваться для передачи больших массивов данных, однако оперативное взаимодействие отдельными сигналами широко используется в управлении вычислениями.

**Уровень комплексируемых каналов ввода-вывода** предназначается для передачи больших объемов информации между блоками оперативной памяти сопрягаемых ЭВМ. Обмен данными между ЭВМ осуществляется с помощью адаптера «канал-канал» и команд «Чтение» и «Запись». Адаптер – это устройство, согласующее скорости работы сопрягаемых каналов. Обычно сопрягаются селекторные каналы машин как наиболее быстродействующие, но можно сопрягать мультиплексные каналы, а также селекторный и мультиплексный. Скорость обмена данными определяется скоростью самого медленного канала. Скорость передачи данных по этому уровню составляет несколько Мбайт/с.

**Уровень управления внешними устройствами** предполагает использование встроенного в устройство управления ВУ (УВУ) двухканального коммутатора и команд «Зарезервировать» и «Освободить». Коммутатор позволяет подключать УВУ одной машины к селекторным каналам различных ЭВМ. По команде «Зарезервировать» канал-инициатор обмена получает доступ через УВУ к любым накопителям на дисках или на магнитных лентах. Обмен канала с накопителями продолжается до полного завершения работ и получения команды «Освободить». Лишь после этого УВУ может подключиться к конкурирующему каналу. Такая дисциплина обслуживания требований позволяет избежать конфликтных ситуаций.

Пять уровней комплексирования получили название логических, так как они объединяют на каждом уровне разнотипную аппаратуру, имеющую сходные методы управления. Каждое из устройств может иметь логическое имя, используемое в прикладных программах. Этим достигается независимость программ пользователей от конкретной физической конфигурации системы. Связь логической структуры программы и конкретной физической структуры ВС обеспечивается операционной системой по указаниям директивам пользователя, при генерации ОС и по указаниям диспетчера-оператора вычислительного центра. Различные уровни комплексирования позволяют создавать самые различные структуры ВС.

Если в составе ВС имеется дорогое уникальное внешнее устройство, то возможно совместное его использование всеми машинами вычислительного комплекса – это еще один уровень комплексирования.

Многомашинные ВС применяются в системах управления сложными объектами. В таких системах с помощью ММС решают две задачи: обеспечение требуемой производительности и надежности. Применение ММС для обеспечения высоких требований по надежности функционирования и по достоверности информации обычно реализуется по следующей схеме.

Машины решают одну и ту же задачу, одновременно выполняя одинаковые операции над одними и теми же данными и периодически сверяя результаты. Если они совпадают, работа ММС продолжается. В случае несовпадения с помощью тестов или по результатам контроля определяется неисправная ЭВМ, ее выходы блокируются и работу системы обеспечивает исправная машина. После ремонта ММС вновь функционирует в нормальном режиме. Для этого в отремонтированную ЭВМ должна быть загружена обновленная информация и вновь обеспечен синхронный режим совместной работы.

Структурная организация ММС сильно зависит от конкретного применения, но можно указать основные концепции их построения:

- многоуровневая иерархическая организация структуры, соответствующая иерархическому характеру комплекса решаемых функциональных задач;

- динамическое перераспределение задач по ресурсам системы;

- модульность структуры и конструкции элементов ВС, обеспечиваемая унифицированной системой модулей и протоколов обмена;

- наличие развитых средств контроля и диагностики.

### План:

- Поток данных и поток команд

- Слабосвязанные и сильносвязанные МКМД-системы

- Кластеры

**Многопроцессорная** система (МПС) – это совокупность процессорных элементов, которые взаимодействуют в процессе решения одной вычислительной задачи под управлением общей операционной системы. Известно много различных структур МПС и несколько принципов их классификации. Наибольшее распространение получила классификация М.Флинна (M.Flynn), построенная на концепции потока.

Если анализировать ВС с точки зрения сочетания потоков данных и потоков команд (понимая под *потоком команд* последовательность команд одной программы, а под *потоком данных* – последовательность данных, обрабатываемых одной программой), то возможны следующие варианты сочетаний:

- 1) одиночный поток команд – одиночный поток данных (ОКОД, или SISD – *Single Instruction Stream/ Single Data Stream*);

- 2) множественный поток команд – одиночный поток данных (МКОД, или MISD – *Multiple Instruction Stream/Single Data Stream*);

- 3) одиночный поток команд – множественный поток данных (ОКМД, или SIMD – *Single Instruction Stream/ Multiple Data Stream*);

- 4) множественный поток команд – множественный поток данных (МКМД, или MIMD – *Multiple Instruction Stream / Multiple Data Stream*).

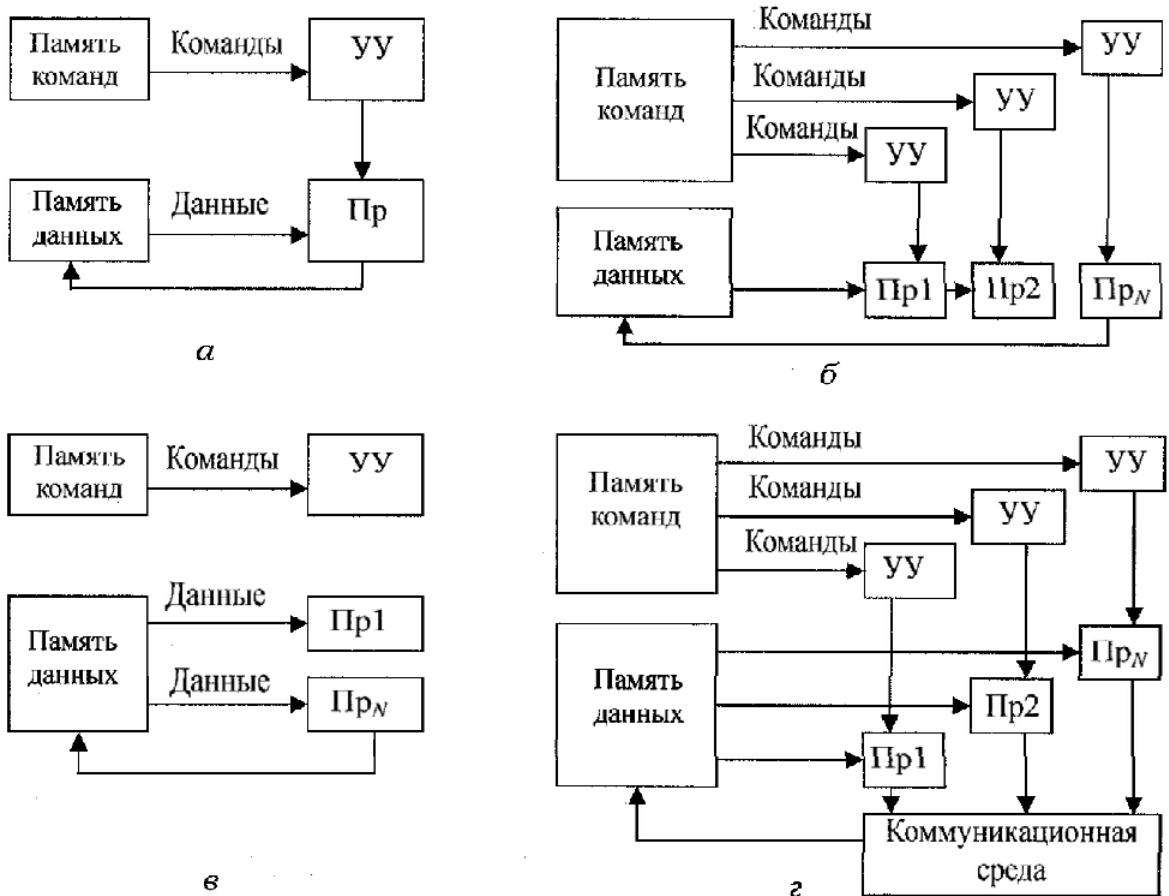

**Архитектура ОКОД** (рис. 4.4.1, а) не представляет интереса для анализа как вычислительная система: это последовательная однопроцессорная скалярная или суперскалярная структура, возможно, с конвейерной обработкой. На одном процессоре выполняется один поток команд; операции выполняются над данными, которые хранятся в одной области памяти. К **архитектуре МКОД** (рис. 4.4.1, б) относят многопроцессорные конвейерные структуры.

Последовательность данных  $D$  передается набору процессоров Пр1, Пр2,...,Пр $p$ , каждый из которых выполняет свою последовательность команд. Примером может служить устройство для сложения двух векторов, компоненты которых – числа с плавающей точкой – последовательно поступают на вход Пр1. Процессоры Пр2, ..., Пр $p$  выполняют операции сравнения порядков, выравнивания, сложения мантисс, нормализации в режиме конвейера (параллельно) над всеми компонентами вектора. Следует заметить, что единого мнения по классу MISD нет: есть утверждения, что подобные структуры на практике еще не были реализованы; возможно, этот класс пуст.

**Архитектура ОКМД** – многопроцессорная матричная структура (рис. 4.4.1, в). Массив процессоров обрабатывает поток команд, поступающих от центрального управляющего устройства. Каждая команда выполняется всеми процессорами одновременно над разными потоками данных.

Примером применения матричной ВС может служить выполнение операций типа вычисления определенного интеграла:

$$\int_a^b y(x)dx \approx h[(y_0/2) + y_1 + y_2 + \dots + y_{n-2} + (y_{n-1}/2)],$$

где  $y_i = y(x_i)$ ,  $x_0 = a$ ,  $x_n = b$ ,  $h = b - a/n$ . Каждый процессор выполняет одну и ту же операцию  $hy(x_i)$ .

Рис. 4.4.1 - Многопроцессорная матричная структура

Главное отличие матричной ВС от векторного процессора заключается в том, что во втором случае высокая производительность обеспечивается с помощью интенсивной конвейеризации, а в первом – за счет высокой степени параллелизма.

Вычислительная система с **архитектурой типа МКМД** (рис. 4.4.1, г) выполняет одновременно и независимо друг от друга несколько программных ветвей с различными наборами данных, обеспечивая в определенные моменты времени обмен данными. В схеме МКМД процессоры должны быть универсальными, поскольку они должны выполнять все команды, необходимые для соответствующего преобразования данных. В классе МКМД различаются слабо- и сильносвязанные системы.

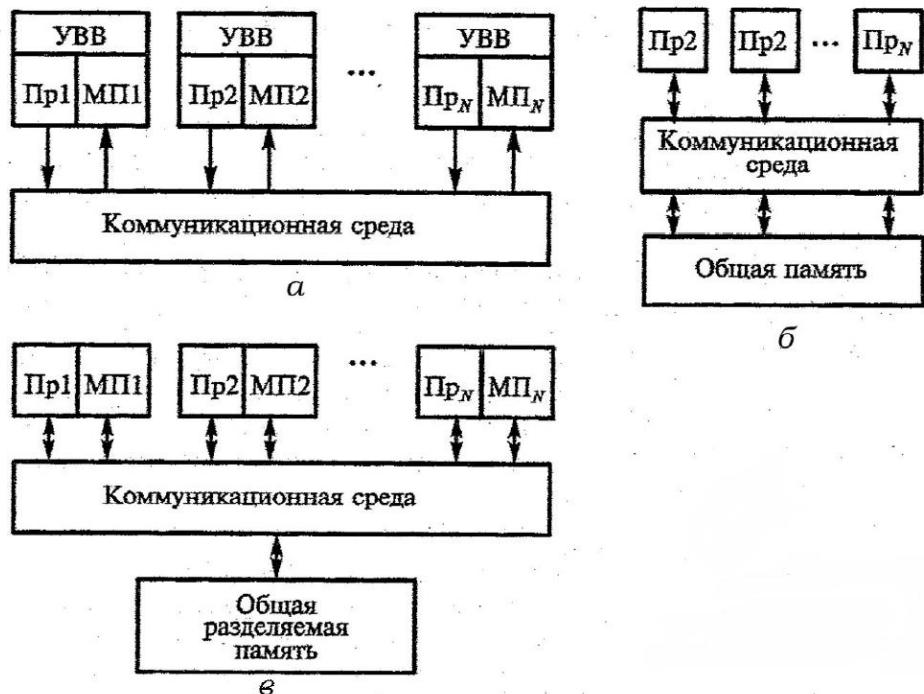

**Слабосвязанные МКМД-системы** – структуры с распределенной памятью. Десять-пятнадцать лет тому назад этот класс ВС состоял исключительно из многомашинных вычислительных комплексов и сетей ЭВМ. Вычислительные системы с такой структурой в качестве узлов используют законченные ЭВМ, включающие микропроцессор, память и подсистему ввода-вывода. Они объединяются коммуникационной средой, которая

обеспечивает взаимодействие процессоров посредством простых операций ввода/вывода (рис. 4.4.2, а). Каждый процессор Пр1,...,Пр $N$  имеет свой модуль памяти и устройство ввода-вывода. Обмен идет через коммуникационную среду.

Рис. 4.4.2 - Взаимодействие процессоров с памятью

Сейчас в качестве элементов МКДМ-систем используются микропроцессоры. Пример современной слабосвязанной МКДМ-системы – Cray T3D/T3E. В нем память физически распределена, так как каждый процессор содержит свою локальную память. В то же время память разделяется всеми процессорами, поскольку каждый из них через свой сетевой интерфейс может обращаться к памяти любого другого процессора, не прерывая его работы. Коммуникации осуществляются с помощью средств операционной системы. Передача данных из одного локального адресного пространства к другому произойдет только в том случае, если посылка сообщения со стороны процесса-отправителя будет востребована процессом-получателем сообщения. В последнее время успехи микроэлектроники сделали возможным построение слабосвязанных систем, состоящих из сотен и тысяч процессорных элементов с возможностью наращивания их количества. Подобные структуры называют **системами с массовым параллелизмом** (MPP-системы – *Mass-Parallel Processing*). Увеличение количества процессорных элементов в ВС не может не привести к росту сложности коммуникационной системы, а также к новым идеям в области управления вычислительным процессом: от управления потоком команд можно перейти к управлению от потока данных, когда операторы программы активизируются по мере готовности данных.

У вычислительных систем с распределенной памятью соотношение цена/производительность ниже, чем у ВС других классов.

Для пользователя еще одно достоинство ВС этого класса заключается в возможности точно подобрать конфигурацию в зависимости от бюджета и своих требований к характеристикам вычислительных средств.

**Сильносвязанные МКМД-системы** – структуры с разделяемой общей памятью. Процессоры совместно используют общую память и каждый из них имеет равные права доступа к программам и данным, которые там хранятся; процессоры могут обмениваться информацией через единое адресное пространство памяти. Такие ВС называются *мультипроцессорными системами с общей памятью*.

Существует два варианта организации общей памяти:

- 1) все процессоры связываются с модулями общей памяти через коммуникационную среду; время обращения к памяти у всех процессоров одинаково и не зависит от того, к какому модулю памяти процессор обращается (см. рис. 4.4.2, б); такие МПС называют *системами с однородным доступом*;

- 2) каждый процессор имеет доступ к общей разделяемой памяти, но, кроме того, он может обращаться и к собственной локальной памяти (см. рис. 4.4.2, в); системы этого типа называют *системами с неоднородным доступом*. Доступ к локальной памяти идет намного быстрее, чем к общей, что повышает производительность ВС. В классе сильносвязанных МКМД-систем выделяют два типа архитектуры: асимметричную и симметричную.

В асимметричной архитектуре разные процессоры могут отличаться как своими характеристиками (производительностью, надежностью, системой команд и т.д.), так и функциональной ролью, которая поручается им в системе. Например, одни процессоры могут предназначаться для работы в качестве вычислительных модулей, другие – для управления вводом/выводом.

Симметричная архитектура предполагает однородность всех процессоров и единство их включения в общую схему МВС.

В качестве проблем, которые характерны для параллельных ВС с общей памятью указываются:

- высокая стоимость;

- неоднородность доступа к памяти: в то время как один процессор обращается к локальной памяти, другой может обращаться к удаленной – время доступа различно и это должно учитываться при организации общего вычислительного процесса;

- необходимость обеспечения согласованности содержимого кэш-памяти.

Сравнение многопроцессорных и многомашинных вычислительных систем приводит к следующим выводам. Многопроцессорные ВС обеспечивают более быстрый обмен между процессорами, более высокую надежность и живучесть по сравнению с ММС.

Однако МПС имеют и существенные недостатки. Они, в первую очередь, связаны с использованием ресурсов общей оперативной памяти. При большом количестве комплексируемых процессоров возможно возникновение конфликтных ситуаций, когда несколько процессоров одновременно обращаются с операциями типа «чтение» и «запись» к одним и тем же областям памяти. Помимо процессоров к общей памяти, подключаются все каналы (процессоры ввода/вывода), средства измерения времени и т.д. Поэтому вторым серьезным недостатком МПС является проблема коммутации абонентов и доступа их к общей памяти.

Создание коммутаторов оперативной памяти представляет сложную техническую задачу: для разрешения конфликтных ситуаций необходимы схемы приоритетного обслуживания; они должны быть дополнены буферами для организации очередей запросов. До настоящего времени в номенклатуре технических средств вычислительной техники отсутствуют высокоеффективные коммутаторы общей памяти.

От того, насколько удачно решаются эти проблемы, и зависит эффективность применения МПС. Это решение обеспечивается аппаратно-программными средствами. Процедуры взаимодействия процессоров очень сильно усложняют структуру операционной системы МПС. Накопленный опыт построения подобных систем показал, что они эффективны при небольшом числе комплексируемых процессоров (от 2 до 10). В отечественных системах «Эльбрус» обеспечивалась возможность работы до 10 процессоров, до 32 модулей оперативной памяти, до четырех процессоров ввода-вывода и до восьми коммутаторов оперативной памяти.

### ***Кластеры***

*Кластером* называют группу взаимосвязанных совместно работающих ЭВМ, представляющих для пользователя единый ресурс, единый центр по обработке информации. В качестве вычислительного узла обычно используются двух- или четырехпроцессорные ЭВМ, хотя могут устанавливаться и однопроцессорные ЭВМ, и локальные сети. Каждый узел работает под управлением своей операционной системы. Состав и мощность узлов могут меняться даже в рамках одного кластера, что дает возможность создавать неоднородные системы. Возможно включение в конфигурацию кластера специализированного компьютера, например, файл-сервера. Поскольку все ЭВМ кластера могут работать самостоятельно и в качестве узлов кластера могут выступать вычислительные системы, то кластер фактически представляет собой вычислительную систему более высокого уровня иерархии.

Концепция кластера появилась как следствие двух факторов:

- 1) стремления повысить производительность вычислительного ресурса, представляемого пользователю.

- 2) потребностью в высоконадежных средствах обработки информации.

Достоинства кластерных структур определяются следующим образом.

1. Можно создавать кластеры любых размеров, превышающие по суммарной производительности любые самые мощные ЭВМ. Кластер может состоять из десятков и сотен ЭВМ, каждая из которых может быть многопроцессорной вычислительной системой. Это свойство наращивать мощность (масштабируемость кластера) обеспечивается аппаратурной, программной и информационной совместимостью его элементов и автоматизацией процесса распределения нагрузки.

2. Пользователь может наращивать технические средства постепенно, и при этом вычислительная мощность кластера будет возрастать линейно, пропорционально приращению характеристик технических средств. Для других типов ВС подобная зависимость имеет нелинейный характер вследствие роста числа конфликтов и усложнения системы обмена.

Возможны два решения проблемы масштабируемости. *Вертикальное* масштабирование осуществляется добавлением ЭВМ, модулей памяти, процессоров и

средств обмена в каждый узел кластера. *Горизонтальное* масштабирование состоит в увеличении числа узлов и в добавлении внешней памяти.

3. Кластер обладает повышенной надежностью и готовностью. Это свойство обеспечивается способностью каждого узла кластера работать автономно, но в любой момент переключаться на выполнение работ другого узла в случае его отказа.

4. Поскольку в качестве «строительных блоков» кластера используются широко распространенные ЭВМ, его стоимость, как правило, меньше стоимости одиночной уникальной ЭВМ с характеристиками, аналогичными обобщенным характеристиками кластера.

Простейший способ обеспечить свойства масштабируемости, надежности и готовности – построить кластер, состоящий из двух узлов, соединенных высокоскоростной линией связи. Эта связь может представлять собой локальную вычислительную сеть, которая используется либо совместно с другими ЭВМ, либо специально для нужд кластера. Дальнейшее развитие этой схемы заключается в дополнительной связи между ЭВМ через дисковую подсистему. Использование избыточной внешней памяти типа RAID (*Redundant Array of Inexpensive Disk* – избыточный массив недорогих дисков) типично для кластеров, оно обеспечивает их высокую надежность.

Для RAID-массивов было разработано шесть разных конфигураций, отвечающих различным задачам. Они названы уровнями RAID, хотя никакой иерархии не представляют. RAID 0 – это базовая конфигурация дискового массива, предназначенная для повышения производительности системы. Один большой файл разбивается на несколько частей, которые записываются на разные диски. Это называется *расслоением данных*. При обращении к такому файлу для чтения диски могут передавать данные параллельно, так что общее время его пересылки сокращается по сравнению со временем пересылки при хранении на одном диске.

Архитектура RAID 1 позволяет повысить надежность хранения данных путем записи их идентичных копий на двух дисках. Такие диски называют *зеркальными*. Если один из них выходит из строя, операции чтения и записи продолжаются с зеркальным диском.

Уровни RAID 2, RAID 3 и RAID 4 предназначены для повышения надежности системы с помощью различных схем контроля четности, не требующих полного дублирования дисков. Вся информация, предназначенная для контроля четности, хранится на диске. В RAID 5 она распределяется между всеми дисками.

Архитектура кластеров используется при построении серверов для распределенных вычислительных систем.

В распределенных ВС появляются распределенные базы данных. Распределенная база данных (РБД) – это база, отдельные части которой размещены (возможно, с дублированием) на нескольких ЭВМ, объединенных сетью. Она должна удовлетворять следующим требованиям:

- быстрая обработка типовых и незапланированных запросов;

- обеспечение безопасности данных;

- обеспечение логической и физической независимости данных;

- обеспечение «прозрачности»:

- распределенной структуры данных (независимость конечных пользователей и программ от варианта размещения информации на ЭВМ сети);

- совместного доступа к данным (поддержка целостности РБД при одновременной модификации одних и тех же данных несколькими пользователями);

- распределенной обработки (независимость конечных пользователей и прикладных программ от типа сети и применяемой сетевой операционной системы).

Администрирование и доступ пользователей к РБД осуществляются с помощью системы управления РБД, которая, исходя из упомянутых требований, обеспечивает выполнение следующих функций:

- автоматическое определение ЭВМ, на которой хранятся требуемые в запросе данные;

- декомпозицию распределенных запросов на частные подзапросы к БД отдельных ЭВМ;

- планирование обработки запросов;

- передачу частных подзапросов и их исполнение на удаленных ЭВМ;

- прием результатов выполнения частных подзапросов, полученных в результате декомпозиции запросов на поиск и чтение данных из РБД, и композицию общего результата;

- поддержание в согласованном состоянии копий дублированных данных на различных ЭВМ сети;

- управление параллельным доступом к РБД многих пользователей;

- обеспечение целостности РБД.

Реализация перечисленных выше функций в распределенной ВС поручается **серверам**. Вообще под термином «сервер» принято понимать объект, предоставляющий сервис другим объектам по их запросам; под *сервисом* понимается процесс обслуживания объектов, а наиболее распространенными видами сервиса являются такие как: хранение и поиск данных; передача сообщений и блоков данных; электронная почта; организация и управление диалогом пользователей; предоставление соединений; проведение сеансов взаимодействия прикладных процессов.

Существует множество типов серверов:

- сервер баз данных, выполняющий обработку запросов, направляемых базе данных;

- файловый сервер, обеспечивающий функционирование распределенных ресурсов, включая файлы и программное обеспечение;

- сервер доступа, обеспечивающий возможность клиенту одной локальной сети связываться с другой сетью;

- коммуникационный сервер, управляющий терминалами и осуществляющий маршрутизацию сообщений.

Распределенные ВС можно строить по принципам, получившим названия «файл – сервер» и «клиент – сервер».

В ВС, построенной по принципу **«файл–сервер»**, файловый сервер не принимает участия в реализации прикладной программы пользователя. Он просто хранит файлы, хотя в ряде случаев служит концентратором для совместного использования периферийных устройств, организуя очереди к периферийным устройствам. Так как файловый сервер является независимым компьютером сети, то его обычно специализируют, устанавливая, например, большой объем дисковой памяти. Функционирующая на рабочей станции прикладная программа считывает и записывает файлы, обмениваясь ими с сетевым файловым сервером, но все операции выполняет самостоятельно.

Во многих случаях файлы передаются по сети между рабочей станцией и сервером целиком, хотя пользователю нужна только их часть. Это приводит к неэффективной загрузке сети. Другой недостаток систем типа «файл – сервер»: в них невозможен одновременный доступ к одному набору данных многими пользователями.

Присущие локальной сети проблемы породили идею кооперативных вычислений по принципу **«клиент–сервер»**. *Клиент* в такой системе – это процесс, который с помощью определенных операций вызывает сервисную функцию. Им может быть программа или пользователь. Сервисная функция в архитектуре «клиент–сервер» описывается комплексом прикладных программ, в соответствии с которым выполняются прикладные процессы. Функции сервера реализуются в виде самостоятельного прикладного процесса либо части общего прикладного процесса. После выполнения каждого задания сервер посыпает результаты клиенту, пославшему это задание.

Функции сети связи известны. В этой системе нагрузка на нее значительно ниже, чем в системе с файловым сервером, поскольку обмен идет не целыми массивами данных, а отдельными фрагментами, например, строками таблицы.

Достоинства системы организации вычислений типа «клиент–сервер» определяются, во-первых, тем, что клиентская и серверная часть могут работать на разных по стоимости и по производительности машинах, что приводит к снижению затрат на систему. Во-вторых, такие системы обладают хорошей адаптацией и гибкостью: замена сервера не приводит к нарушению клиентских приложений, а расширение числа пользователей (в определенных пределах) не влияет на работу сервера. В-третьих, каждый функциональный элемент, в том числе и клиентское приложение, легко может быть специализировано для выполнения тех или иных специфических функций.

По общему признанию, вычисления по схеме «клиент–сервер» более дешевые по сравнению с централизованными системами с большими ЭВМ.

В то же время нельзя забывать о том, что отказы сервера делают всю систему неработоспособной, а применение этой схемы для системы, обрабатывающей сотни и тысячи одинаковых приложений (типа заказов билетов), сводят на нет все ее достоинства.

## ГЛАВА-IV. ПРОЦЕССОРЫ

### ЛЕКЦИЯ 4.1. АРХИТЕКТУРА ПРОЦЕССОРОВ.

---

#### План:

- CISC и RISC процессоры

- Конвейеризация

- Основные черты RISC архитектуры

- Кэш память

- Поддержка многозадачности и многопроцессорности

#### *CISC и RISC процессоры*

Основной временной характеристикой для процессора является время цикла, равное  $1/F$ , где  $F$  - тактовая частота процессора. Время, затрачиваемое процессором на задачу, может быть вычислено по формуле  $C * T * I$ , где  $C$  - число циклов на одну инструкцию,  $T$  - время на один цикл,  $I$  - число инструкций на задачу.

Разработчики “классических” систем (которые теперь называют CISC (Complete Instruction Set Computer)) стремились уменьшить фактор  $I$ . В процессорах реализовывались все более сложные инструкции, для выполнения которых внутри него самого запускались специальные процедуры (так называемый микрокод), загружаемые из ПЗУ внутри процессора. Этому пути способствовало то, что улучшения в технике производства полупроводников делали возможным реализацию все более сложных интегрированных цепей. Однако, на этом пути очень трудно уменьшить два других фактора:  $C$  поскольку инструкции сложные и требуют *программного декодирования* и  $T$  в силу *аппаратной сложности*.