# **Микропроцессорные устройства и системы управления на железнодорожном транспорте**

**Лабораторные работы**

**Ташкент– 2013**

ГАЖК “Ўзбекистон темир йўллари”

Ташкентский институт инженеров железнодорожного транспорта

## **Микропроцессорные устройства и системы управления на железнодорожном транспорте**

Методические указания по выполнению лабораторных работ для

подготовки бакалавров 3 и 4-го года обучения по направлениям

5311000 – «Автоматизация и управление технологических процессов и

производство (железнодорожный транспорт)»

5111000 – «Профессиональное образование (5311000 –

«Автоматизация и управление технологических процессов и производство

(железнодорожный транспорт)»)»

Ташкент– 2013

УДК 621.31

Методические указания к выполнению лабораторных работ по дисциплине «Микропроцессорные устройства и системы управления на железнодорожном транспорте» предназначены для студентов бакалавриата направлений 5311000 – «Автоматизация и управление технологических процессов и производство (железнодорожный транспорт)», 5111000 – «Профессиональное образование (5311000 – «Автоматизация и управление технологических процессов и производство (железнодорожный транспорт)»)». Указания предназначены для оказания методической помощи при проведении лабораторных работ по изучению принципов построения и работы цифровых устройств разного назначения таких как триггеры, регистры, шифраторы, дешифраторы и микросхемы памяти

Рекомендованы к изданию решением Учебно-методической комиссии Ташкентского института инженеров железнодорожного транспорта

Составители: - кандидат технических наук, доцент Азизов А.Р.;

- ассистент Юлдашев Ш.М.

Рецензенты: - начальник отдела СЦБ «Центра сигнализации и связи» ГАЖК «Узбекистон Темир Йуллари» Хасанов Н.Т.

- кандидат технических наук, доцент кафедры «Автоматика и телемеханика на ж.-д. транспорте» Хорунов Ш.Р.

# Лабораторная работа №1

## Изучение работы триггеров различных типов

**1. Цель работы:** изучение основных типов триггеров

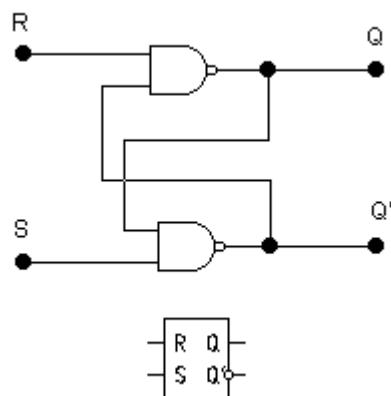

**2. Общие сведения.** Триггер предназначен для хранения одной логической переменной. В соответствии с этим триггер имеет два состояния. Одно из них обозначается как состояние 0, другое как состояние 1. Воздействуя на входы триггера, его устанавливают в нужное состояние. Триггеры широко используются во многих узлах электронной аппаратуры как самостоятельные схемы, а также в качестве базовых элементов для построения цифровых устройств. R-S триггер представляет собой симметричную структуру, состоящую из двух логических элементов ИЛИ –НЕ или И-НЕ, охваченных перекрестной положительной обратной связью. Триггер на элементах И-НЕ собранный в программе EWB показан на рис1.

Рис. 1. Принципиальная схема и условное обозначение R-S триггера

Такой триггер называется симметричным, он может использоваться как бистабильная ячейка, ячейка памяти. Переключение триггера из одного устойчивого состояния в другое происходит при подаче активных сигналов на входы R-S. При подаче на вход R уровня логической 1 первый элемент устанавливается в состояние, в котором на его прямом выходе действует уровень логического 0, следовательно на инверсном -1 такое состояние триггера считается установкой в 0. Если триггер до подачи сигнала находился в состоянии 1, то при подаче на вход R уровня логического 0 триггер изменит состояние на противоположное. Такое состояние триггера называется установкой в 0. Процесс установления триггера в состояние 1 при подаче на его вход S=1 аналогичен. Одновременная подача уровней лог.1 на оба входа R и S не допускается, так как при этом на обоих входах

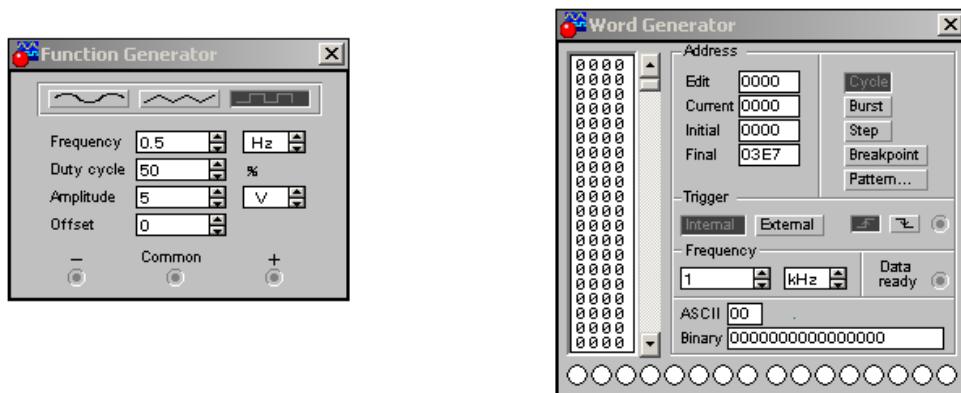

установится уровень лог. 0, а после снятия со входов активных логических уровней состояние триггера окажется неопределенным. Исследование R-S триггера в программе EWB производится при помощи генератора ( Function Generator) и генератора слова ( Word Generator) (рис 2.), которые выбираются в каталоге программ.

Рис. 2. Изображение генераторов в среде EWB

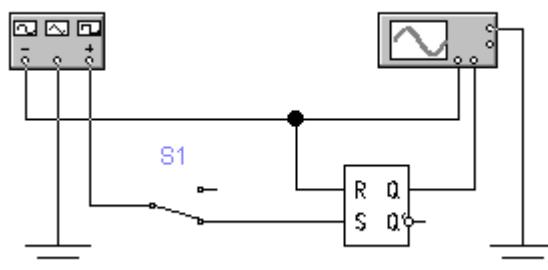

Схема подключения RS триггера к осциллографу и генератору показана на рис 3.

Рис. 3. Схема подключения RS триггера

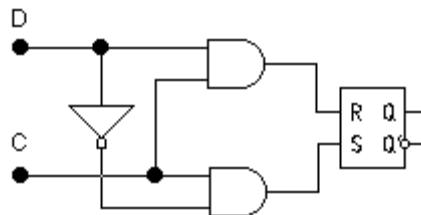

2 - D - триггер в отличие от R-S имеет для установки в состояния 0 и 1 один информационный D вход D- триггер образуется из R-S триггера если на информационные входы одновременно подать инверсные сигналы.

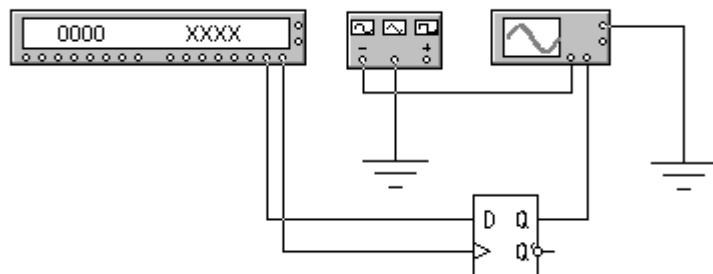

Исследование D триггера производится по схеме рис. 5 в следующем порядке: 1 – на входы установки триггера от генератора подаются соответствующие активные сигналы 0 или 1 и далее состояние триггера фиксируется по окну осциллографа.

Рис. 4. Схема преобразования R-S триггера в D - триггер

Рис 5 Схема изучения D - триггера

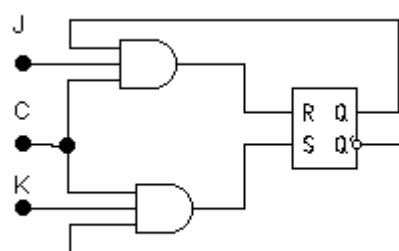

JK – триггер. Особенностью JK триггера является то, что при всех комбинациях входных сигналов, кроме  $J= K=1$  он срабатывает подобно R-S триггеру в каждом такте происходит опрокидывание триггера и выходные сигналы меняют свои значения. Это является универсальным свойством JK триггера и дает возможность использовать его как основу для построения основных функциональных схем: счетчиков, регистров.

На рис. 6 показана схема JK триггера, собранная на основе RS триггера. Схема исследования J-K триггера в программе EWB представлена на рис .7.

Рис.6. Схема JK триггера собранная на основе RS триггера

### 3. Описание рабочего места

Рабочим местом является ПЭВМ, имеющей в своем арсенале специализированное программное обеспечение EWB.

#### **4. Задание на лабораторную работу**

1. Ознакомиться с работой специализированного программного обеспечения EWB.

2. Проследить за работой устройства в среде EWB.

3. Проследить за работой изучаемых триггеров с помощью осциллографа.

4. Заполнить таблицу переходов всех триггеров.

5. Определить точки соприкосновения и различить в изучаемых триггерах.

Рис .7. Схема J-K триггера с подключением генератора, осциллографа в программе EWB

#### **5. Указание к выполнению лабораторной работы**

Ознакомиться и научиться работать со специализированным программным обеспечением EWB. Набрать схемы в среде EWB согласно рис.3, 5 и 7. Задайте параметры работы генератора импульсов (рис.2.). При изучении работы R-S (рис.3) необходимо вручную с помощью ключа подавать импульсы на вход триггера. Поочередно изучить работы J-K триггеров

#### **6. Содержание отчета**

В соответствии с заданием в отчёте должны быть представлены:

1. Краткое описание работы R-S, D и J-K триггеров.

2. Схемы реализации работы R-S, D и J-K триггеров согласно задания.

3. Полученные в результате работы таблицы истинности для R-S, D и J-K триггеров.

4. Алгоритмы работы изучаемых R-S, D и J-K триггеров.

5. Описание работы устройств в среде EWB.

#### **Контрольные вопросы**

1. Что такое триггер, при решении каких задач он используется?

2. Как работает R-S триггер?

3. Как работает D триггер?

4. Как работает J-K триггер?

4. Какие логические элементы могут использоваться для построения R-S, D и J-K триггеров?

5. Какие микросхемы выполняют функции R-S, D и J-K триггеров?

## Лабораторная работа № 2

### Изучение работы шифраторов и дешифраторов

**1. Цель работы:** изучение принципа работы, построения и применения шифраторов и дешифраторов в цифровых устройствах.

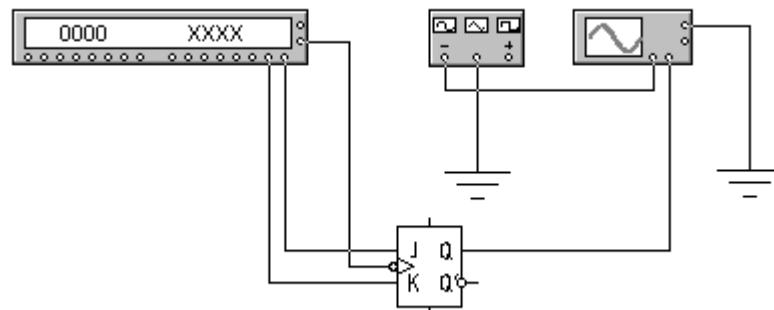

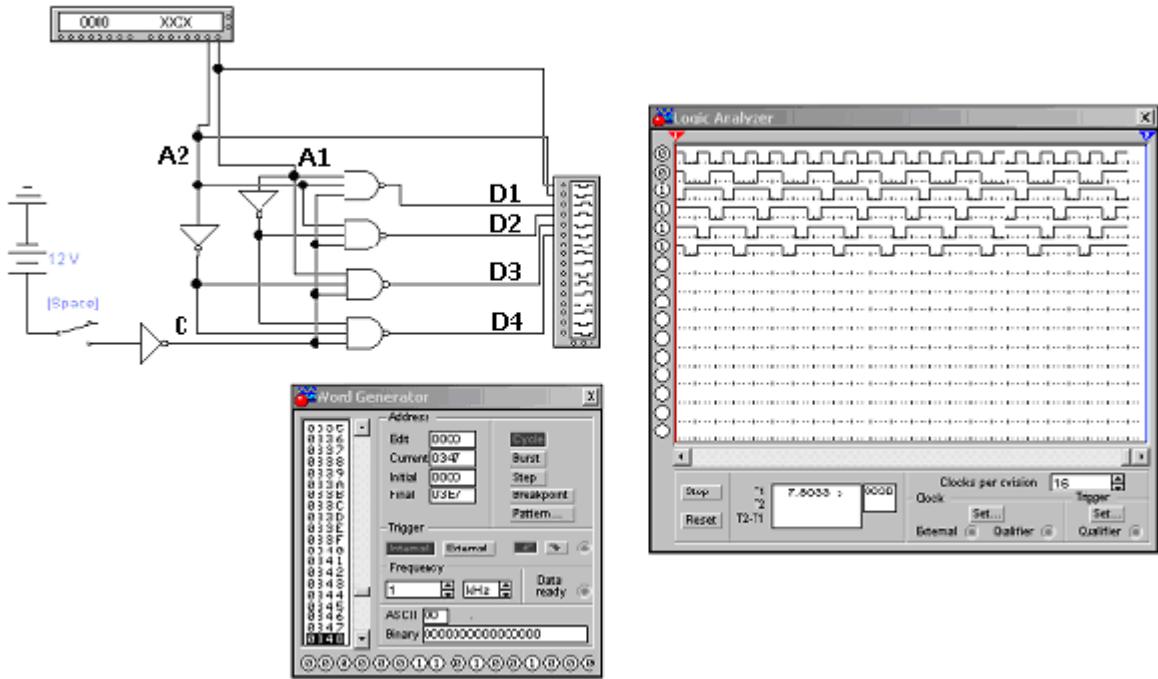

**2. Общие сведения.** Шифраторы (кодер) осуществляет преобразование десятичных чисел в двоичную систему счисления. Подача сигнала на один из входов приводит к появлению на выходах  $n$ -разрядного двоичного числа, соответствующего номеру возбужденного входа. Шифраторы широко используются в разнообразных устройствах ввода информации в цифровые системы. Для ввода информации используется клавиатура. Нажатие десятичной клавиши соответствует генерации соответствующего кода. Поскольку в клавиатуре невозможно нажатие сразу нескольких клавиш, в шифраторах используется принцип приоритета старшего разряда т.е. при нажатии, например, клавиш 9,5, 2 на выходе шифратором будет генерироваться код 1001, соответствующий 9 . Шифратор может быть построен на практических всех представленных в библиотеке EWB логических элементах, кроме этого в библиотеке программы имеется микросхема ИМС-74148, что соответствует аналогу ИМС-155ИВ1 – шифратор приоритетов. Пример построения схемы шифратора на ИМС- 74148 показан на рис. 12 Дешифратор предназначен для обратного преобразования двоичных чисел в десятичные. Дешифраторы, как самостоятельные изделия электронной техники изготавливаются на 4, 8, 16 выходов. При необходимости количество входов наращивается. В качестве примера рассмотрим построение дешифратора элементах И-НЕ для подачи информационных сигналов на входы дешифратора используется логический генератор слова (рис 9). Схема дешифратора содержит три инвертора и четыре элемента ЗИ-НЕ .

### **3. Описание рабочего места**

Рабочим местом является ПЭВМ, имеющей в своем арсенале специализированное программное обеспечение EWB.

#### 4. Задание на лабораторную работу

1. Ознакомиться с работой специализированного программного обеспечения EWB.

2. Собрать схемы рис. 8 и 9.

3. Проследить за работой шифратора и дешифратора в среде EWB.

4. Провести моделирование работы шифратора в соответствии с таблицей истинности и дешифратора с двумя входами и четырьмя выходами в программе EWB.

5. Модернизируйте схему дешифратора 2\*4 с использованием логического преобразователя и генератора слова библиотеки EWB, дополнив ее еще одним входом, проведите испытание .

6. Построить дешифратор с 4 входами и 16 выходами.

Рис.8. Схема шифратора на ИМС- 74148

| Inputs |   |   |   |   |   |   |   | Outputs |    |    |    |    |    |

|--------|---|---|---|---|---|---|---|---------|----|----|----|----|----|

| EI     | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7       | A2 | A1 | A0 | GS | EO |

| 1      | X | X | X | X | X | X | X | X       | 1  | 1  | 1  | 1  | 1  |

| 0      | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1       | 1  | 1  | 1  | 1  | 0  |

| 0      | X | X | X | X | X | X | X | 0       | 0  | 0  | 0  | 0  | 1  |

| 0      | X | X | X | X | X | X | 0 | 1       | 0  | 0  | 1  | 0  | 1  |

| 0      | X | X | X | X | X | 0 | 1 | 1       | 0  | 1  | 0  | 0  | 1  |

| 0      | X | X | X | X | 0 | 1 | 1 | 1       | 0  | 1  | 0  | 0  | 1  |

| 0      | X | X | X | 0 | 1 | 1 | 1 | 1       | 1  | 0  | 0  | 0  | 1  |

| 0      | X | X | 0 | 1 | 1 | 1 | 1 | 1       | 1  | 0  | 1  | 0  | 1  |

| 0      | X | 0 | 1 | 1 | 1 | 1 | 1 | 1       | 1  | 0  | 1  | 0  | 1  |

| 0      | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1       | 1  | 1  | 1  | 0  | 1  |

Рис. 9. Схема дешифратора собранная на элементах И-НЕ.

## 5. Указание к выполнению лабораторной работы

Ознакомиться и научиться работать со специализированным программным обеспечением EWB. Набрать схемы в среде EWB согласно рис. 8 и 9. При изучении работы шифратора рис.8, необходимо вручную с помощью переключателей подавать на информационные входы шифратора различные комбинации в соответствии с таблицей истинности. При изучении работы рис. 9 дешифратора необходимо вручную с помощью переключателя подавать импульсы на вход триггера.

## 6. Содержание отчета

В соответствии с заданием в отчёте должны быть представлены:

1. Краткое описание работы шифратора и дешифратора

2. Схемы реализации работы шифратора и дешифратора согласно задания.

3. Полученные в результате работы таблицы истинности для шифратора и дешифратора.

4. Алгоритмы работы изучаемых устройств.

5. Описание работы устройств в среде EWB.

## Контрольные вопросы

1. Что такое шифратор, при решении каких задач он используется?

2. Какой дешифратор называется линейным?

3. Какой дешифратор называется прямоугольным?

4. Какие логические элементы могут использоваться для построения дешифратора и шифратора?

5. Какие микросхемы выполняют функции шифратора и дешифратора?

## Лабораторная работа № 3

### Изучение работы регистров

**1. Цель работы:** изучить работу регистров последовательного и параллельного типов.

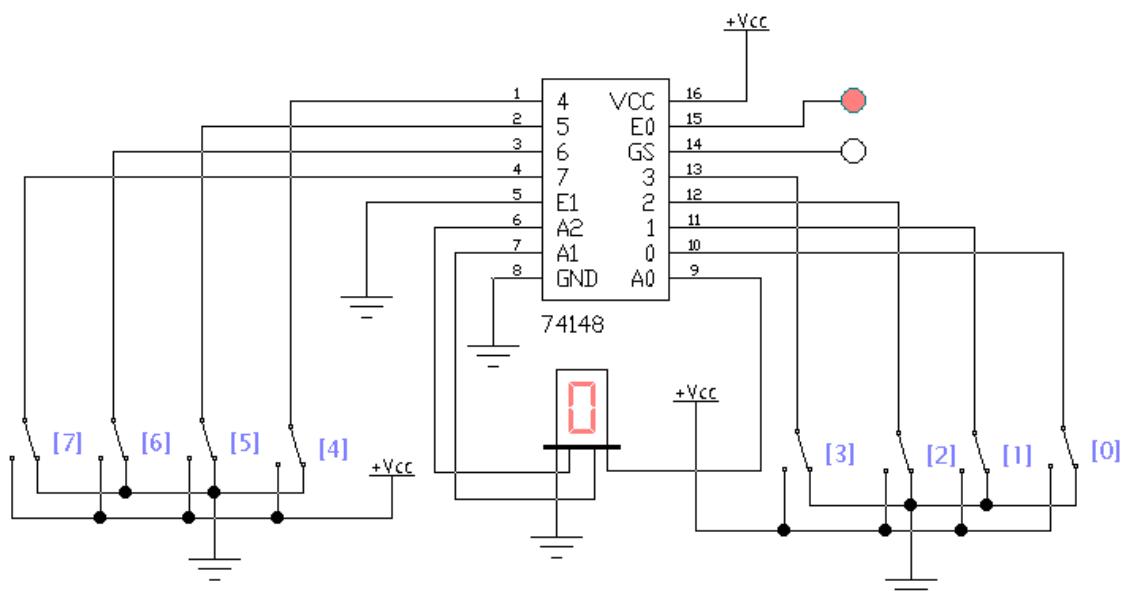

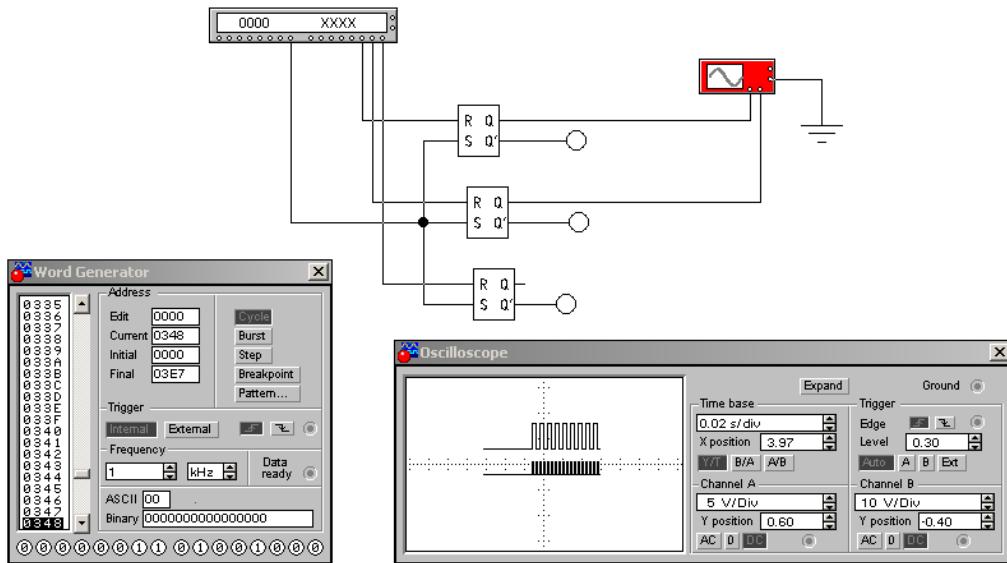

**2. Общие сведения.** Регистры - это устройства предназначенные для хранения и преобразования многоразрядных двоичных чисел. Они используются в качестве управляющих и запоминающих устройств. Регистры выполняются на триггерах типа D или JK, одиночный триггер запоминает один разряд двоичной информации 1-бит. Занесение информации в регистр называется операцией ввода информации. Выдача информации называется операцией вывода или считывания, запись новой информации в регистр требует его предварительного обнуления. В зависимости от функциональных свойств регистры подразделяются на накопительные регистры, регистры памяти, хранения и сдвигающие. Сдвигающие регистры подразделяются: по способу ввода и вывода информации на параллельные, последовательные и комбинированные; по направлению передачи информации – односторонние и реверсивные. Регистры памяти предназначены для хранения в течении короткого промежутка времени. Ввод и вывод информации в такой регистр производится параллельным кодом. С приходом очередного тактового импульса записанная информация обновляется. Регистры хранения представляют собой набор триггеров с независимыми информационными входами и общим тактовым входом. Наращивание разрядности регистра осуществляется добавлением определённого числа триггеров. В регистрах памяти тактовые входы всех триггеров подсоединены к шине синхронизации, что даёт возможность хранить информацию до появления импульса синхронизации. На рис.10 представлен пример построения регистра хранения информации на библиотечных D триггерах в программе EWB. Выход триггера каждого разряда подключен к входу D триггера соседнего более младшего разряда. Таким образом, при низком уровне синхронизирующего сигнала хранящееся в триггере

значение разряда числа передается на вход триггера соседнего справа разряда и производит в нем подготовку управляющих цепей. В момент положительного фронта синхронизирующего сигнала каждый из триггеров устанавливается в состояние, соответствующее действующему на входе D сигналу, и число в регистре оказывается сдвинутым на один разряд вправо. Для осуществления сдвига влево необходимо в сдвиговом регистре изменить связи между триггерами, подключая выход триггера к входу D триггера соседнего более старшего разряда. В параллельном регистре предназначеннное для хранения число подается одновременно всеми разрядами т.е. в параллельной форме. При этом для каждого разряда числа предусматривается два входа, на один из которых поступает прямой код, на другой- инверсный. Пример построения такого регистра на R-S триггерах показан на рис. 11.

### 3. Описание рабочего места

Рабочим местом является ПЭВМ, имеющей в своем арсенале специализированное программное обеспечение EWB.

### 4. Задание на лабораторную работу

1. Построить 8 разрядный параллельный регистр.

2. Построить схему 4 разрядного сдвигающего регистра на D триггерах

Рис. 10. Схема построение регистров хранения информации на основе D – триггерах

Рис.11. Схема параллельного регистра на RS – триггерах

3. Пояснить принцип работе регистра на примере продвижения единицы, построить временные диаграммы сигналов на выходах регистра.

### 5. Указание к выполнению лабораторной работы

1. Ознакомиться и научиться работать со специализированным программным обеспечением EWB.

2. Набрать схемы в среде EWB согласно рис. 10 и 11

3. Для изучения работы последовательного регистра рис.10, необходимо с помощью генератора прямоугольных импульсов подавать на информационные входы последовательного регистра различные комбинации и наблюдать с помощью индикатора зарегистрированную информацию.

4. Для изучения работы параллельного регистра рис. 15 необходимо с помощью генератора прямоугольных импульсов подавать импульсы на вход регистра.

### 6. Содержание отчета

В соответствии с заданием в отчёте должны быть представлены:

1. Краткое описание работы регистров.

2. Схемы реализации работы последовательного и параллельного регистров в соответствии с заданием.

3. Алгоритмы работы изучаемых устройств.

4. Построенные временные диаграммы сигналов на выходах регистрации при подаче шести сдвигающих импульсов.

5. Описание работы устройств в среде EWB.

## **Контрольные вопросы**

1. Что из себя представляет регистр?

2. Перечислите типы регистров?

3. На чем основан принцип работы регистра на примере продвижения одной единицы?

4. Можно ли в регистре использовать J-K триггеры?

5. Как можно использовать регистр в качестве распределителя импульсов (пояснить схемой)?

## **Лабораторная работа № 4**

### **Изучение работы микросхемы памяти**

**1. Цель работы:** изучение основных принципов построения запоминающих устройств статического и динамического типов, овладение практическими методами записи и считывания, редактирования и программирования запоминающих устройств (ЗУ).

**2. Общие сведения.** В МП системах для хранения программ и данных используются полупроводниковые устройства, которые можно разделить на два класса: постоянные запоминающие устройства (ПЗУ) для хранения программ (информация в них сохраняется при отключении питания) и оперативные запоминающие устройства (ОЗУ) для хранения данных (информация в них теряется при выключении питания). Из ПЗУ в процессе выполнения программы производится только считывание информации. При этом содержимое всех ячеек памяти остается неизменным. Считывание каждой ячейки происходит без разрушения информации неограниченное число раз. Процесс занесения информации в такие ЗУ называется программированием микросхемы. Микросхемы могут программироваться однократно при изготовлении (так называемые масочные ПЗУ) или разработчиком с использованием специальных технических средств (программаторов). Существуют ПЗУ, в которых информацию можно стереть и записать новую (ПЗУ с ультрафиолетовым или электрическим стиранием). ОЗУ, представляющие собой матрицы активных энергозависимых ячеек, позволяют записывать и считывать информацию в процессе выполнения программы из любой ячейки памяти. ОЗУ бывают статического и динамического типов. Статические ОЗУ создаются на базе триггеров, каждый из которых может хранить один бит информации (логический «0» или логическую «1»). В динамическом ОЗУ информация хранится за счет паразитных емкостей МОП-

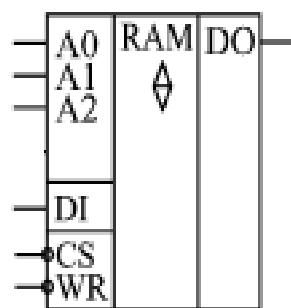

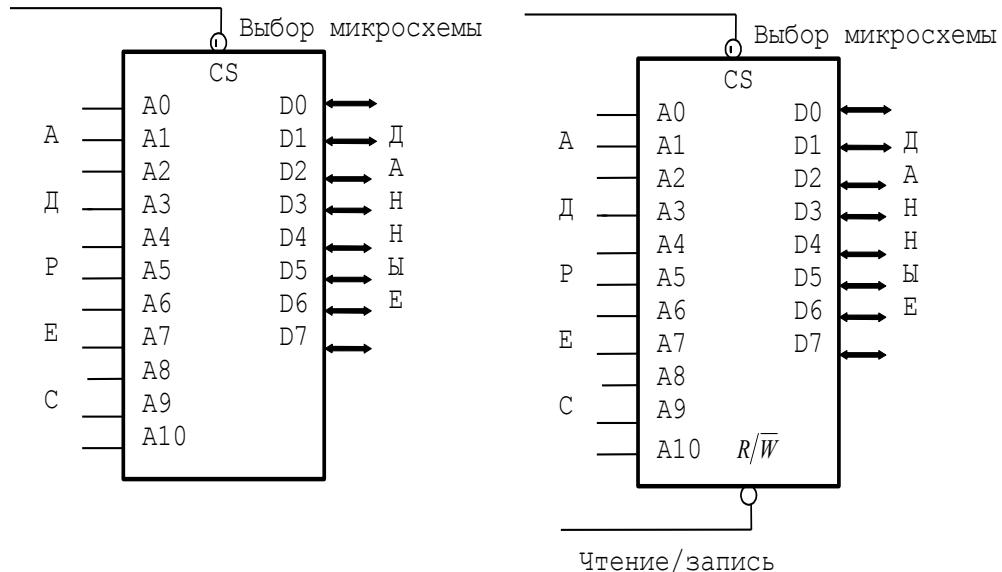

транзисторов. На рис.12 схематически показано ОЗУ статического типа емкостью 8 бит (реальные ОЗУ имеют значительно большую емкость, например 64 Кбайта = 65536 ячеек по 8 разрядов и выше). Число ячеек памяти в ЗУ зависит от числа адресных линий. Например, при двухадресной шине можно выбрать одну из четырех ячеек, имеющую адрес 00, 01, 10 или 11. В общем случае, число адресуемых ячеек равно  $2^N$ , где N - количество адресных линий. Число разрядов в каждой ячейке ЗУ зависит от типа микросхемы (может быть 1, 4, 8, 16 бит). На рис. 17 приведены примеры реально выпускаемых микросхем ПЗУ емкостью 2 Кбайта (2048 ячеек по 8 бит) и ОЗУ емкостью 1 Кбайт (1024 ячейки по 8 бит). При поступлении сигнала на вход ВЫБОР КРИСТАЛЛА ( $\overline{CS} = 0$ ) открываются выходные формирователи с тремя состояниями, и информация из выбранной ячейки поступает на ШД (рис. 17). Если сигнал  $CS = 1$ , информационные выходы D0 - D7 переходят в третье состояние, микросхема «отключается» от ШД.

Поскольку в ОЗУ (рис. 17) информация может не только считываться, но и записываться, микросхема имеет дополнительную линию управления  $READ/\overline{WRITE}$  ( $R/\overline{W}$ ). При сигналах  $R/\overline{W} = 0$  и  $\overline{CS} = 0$ , информация присутствующая на ШД записывается в выбранную ячейку памяти (выбор происходит адресом на ША). При сигналах  $R/\overline{W} = 1$  и  $\overline{CS} = 0$  открывается выходной формирователь с тремя состояниями и информация из выбранной ячейки (ее адрес на ША) через выходы D0 - D7 передается на ШД. В лабораторной работе представлены программно реализованные модели оперативных запоминающих устройств статического типа.

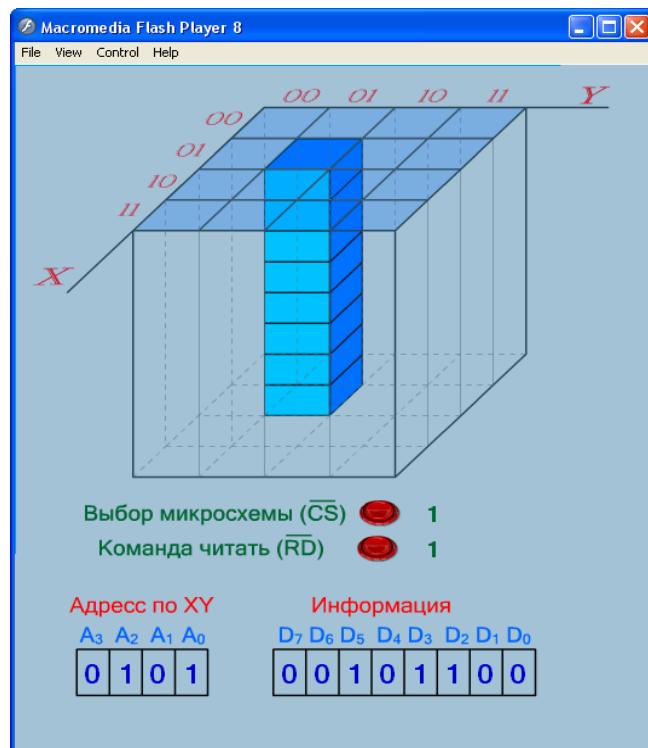

Рис. 12 Структура ОЗУ на 8 бит

Рис.13. Микросхемы ПЗУ и ОЗУ

Лабораторная работа состоит из двух частей: в первой изучается анимационная модель статического запоминающего устройства, а также принцип объединения отдельных устройств для построения памяти большой емкости; во второй исследуются особенности работы статической памяти в программном пакете Proteus 7.0.

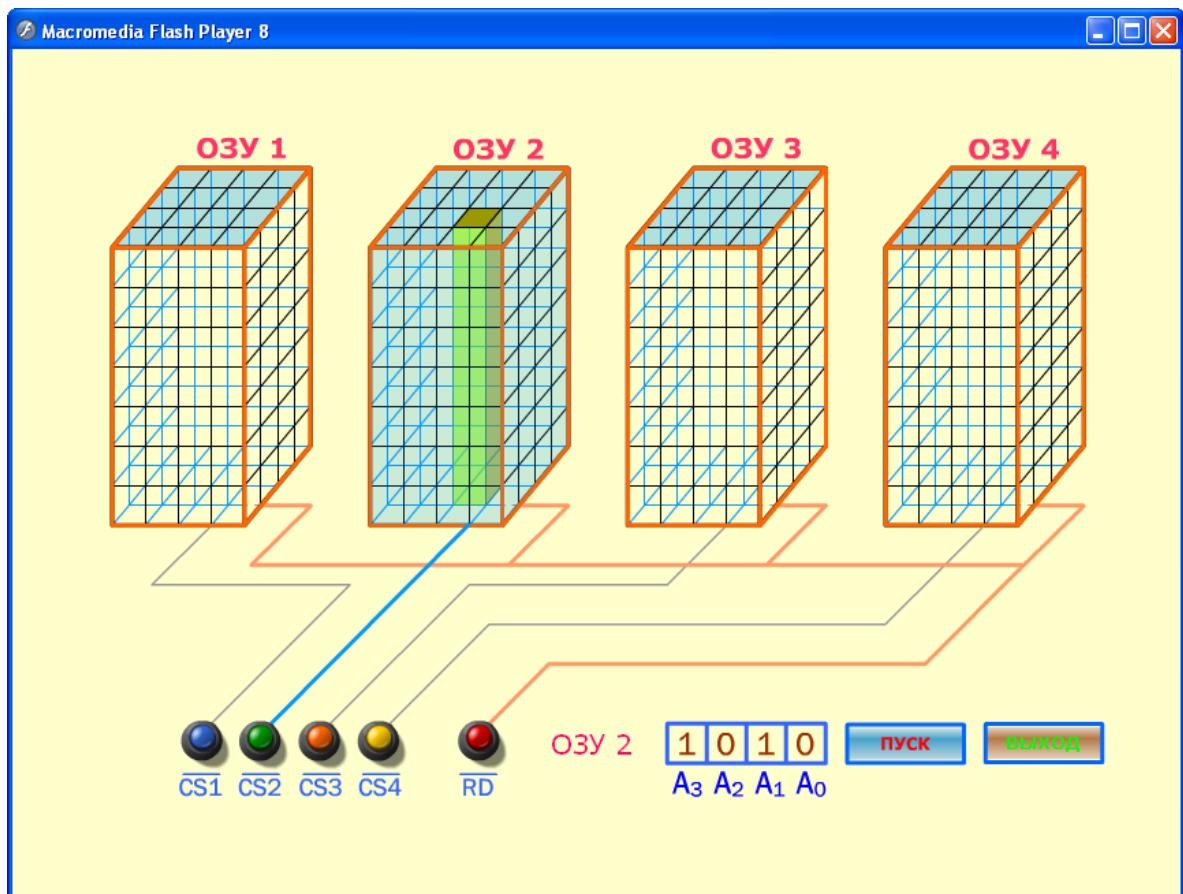

Программная анимационная модель статического оперативного запоминающего устройства представляет собой традиционную структуру ЗУ с произвольной выборкой, состоящую из дешифраторов строк и столбцов и матрицы накопительных элементов. При выполнении работы имитируются режимы записи и чтения данных для любой ячейки памяти. На рис.14 показана анимационная модель ячейки ОЗУ. Чтобы имитировать режим чтения данных с ячейки ОЗУ, необходимо подать на выводы CS и RD логическую 1. После чего с помощью компьютерной мыши можно будет выбрать нужную ячейку ОЗУ. На основании координаты из адреса XY считывается информация, показанная в ячейках D7 – D0. На рис.15 показана анимационная модель модуля ОЗУ. Чтобы имитировать режим чтения данных с нужной микросхемы ОЗУ, необходимо подать на вывод RD логическую 1 и в соответствующую микросхему ОЗУ на вывод CS подать логическую 1.

После чего нужно набрать на ячейках A3 – A0 необходимый адрес. Далее нажимаем кнопку ПУСК. Начинается имитация режима считывания информации с модуля ОЗУ.

### **3. Описание рабочего места.**

Рабочее место представляет собой компьютер со специализированным программным пакетом PROTEUS PROFESSIONAL и виртуальной анимационной моделью ячейки памяти.

### **4. Задание к выполнению работы**

4.1. Изучить режимы работы запоминающих устройств на виртуальной модели.

4.2. Исследовать работу ОЗУ в режиме считывание информации.

4.3. Исследовать работу ОЗУ в режиме записи информации.

### **5. Порядок выполнения работы**

1. Загрузить на компьютере PROTEUS PROFESSIONAL.

2. Ознакомиться с методическими указаниями.

3. Изучить работу ОЗУ (рис.14) и модуля ОЗУ (рис. 15) на виртуальной модели.

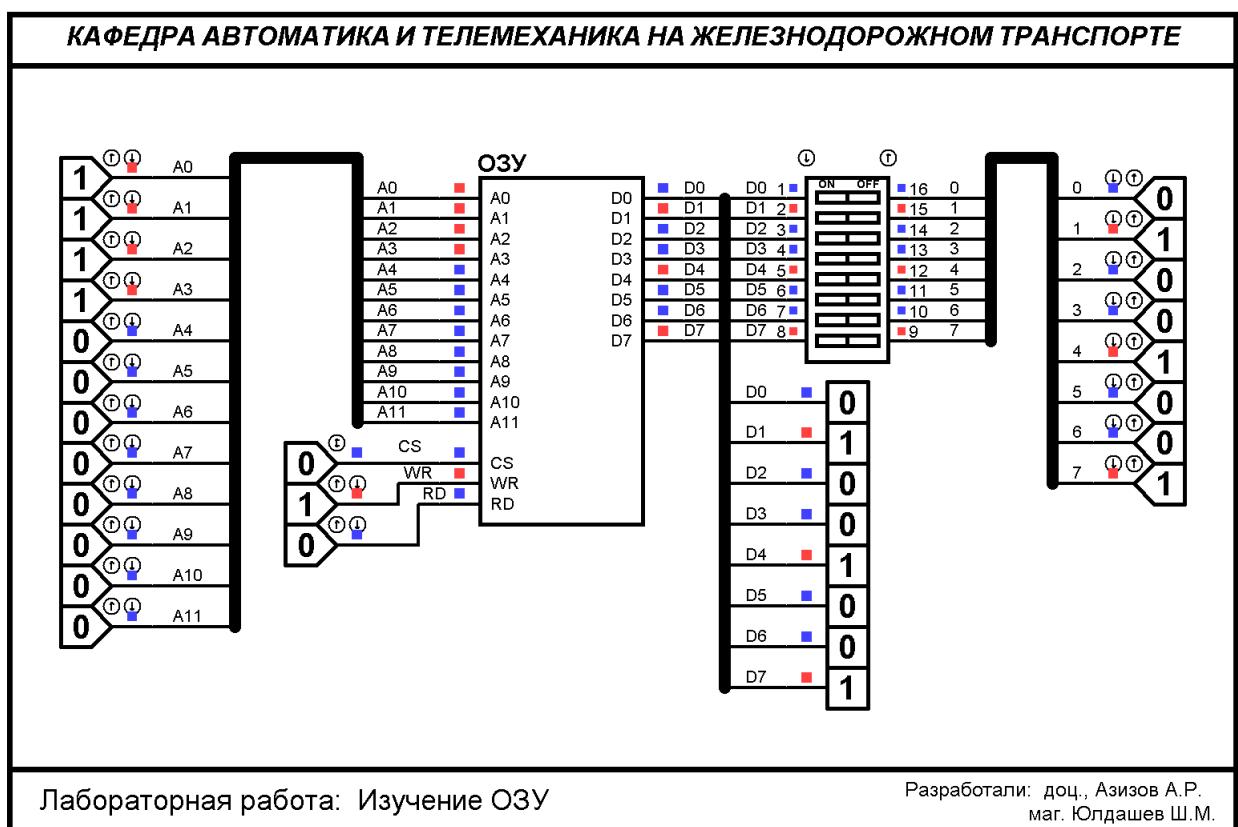

4. Исследовать работу ОЗУ в режиме записи и считывания информации (рис. 16).

5. Для задания кода адреса ОЗУ используются двенадцать кнопок с фиксацией A0 - A11. Отжатому состоянию кнопки соответствует сигнал логического "0", нажатому состоянию - сигнал логической "1" (при этом загорается соответствующий цвет на самой кнопке. Красный цвет - логический 1, синий цвет – логический 0).

6. Данные для записи в ОЗУ формируются с помощью переключателя SW1. Число импульсов задается при помощи восьми кнопок с фиксацией D0 – D7. При записи информации в ОЗУ кнопка SW1 должна находиться в состоянии ON. Кнопка SW1 выполняет функции коммутатора при записи (считывание) информации в ОЗУ.

7. При подаче на управляющие выводы CS – 1, RD – 0, WR – 1, в выбранной ячейке ОЗУ записывается информация из шины данных.

8. При считывании информации с ОЗУ кнопка SW1 должна находиться в состоянии OFF.

9. При подаче на управляющие выводы CS – 1, RD – 1, WR – 0 с выбранной ячейки ОЗУ считывается информация с шины данных и имитируется на логических анализаторах.

### **6. Содержание отчета**

1. Название и цель работы.

2. Основные характеристики исследуемого ОЗУ.

3. Функциональная схема исследуемого устройства.

4. Выводы.

## Контрольные вопросы

1. Поясните принцип работы ячейки динамического ОЗУ.

2. Начертите временные диаграммы записи и считывания.

3. Поясните работу ячейки ОЗУ п- и К-МОП.

4. Как производится выборка ячейки ОЗУ?

5. Как осуществляются запись и считывание?

6. От чего зависит энергопотребление ОЗУ?

7. Начертите временные диаграммы работы ОЗУ.

8. Поясните принцип работы ячейки ПЗУ.

9. Как осуществляется стирание информации?

Рис.14. Анимационная модель ячейки ОЗУ

Рис.15. Анимационная модель модуля ОЗУ.

Рис 16. Виртуальная модель микросхемы ОЗУ

ГАЖК “Ўзбекистон темир йўллари”

Ташкентский институт инженеров железнодорожного транспорта

**Разрешаю в печать**

Проректор по учебной работе

**доцент**

**Ф. Каримова**

«\_\_\_\_» \_\_\_\_\_ 20\_\_ г.

## **Микропроцессорные устройства и системы управления на железнодорожном транспорте**

Методические указания по выполнению лабораторных работ для

подготовки бакалавров 3 и 4-го года обучения по направлениям

5311000 – «Автоматизация и управление технологических процессов и

производство (железнодорожный транспорт)»

5111000 – «Профессиональное образование (5311000 – «Автоматизация и

управление технологических процессов и производство

(железнодорожный транспорт)»)»

Ташкент– 2013

## СОДЕРЖАНИЕ

|                                                                        |    |

|------------------------------------------------------------------------|----|

| Лабораторная работа №1. Изучение работы триггеров различных типов..... | 3  |

| Лабораторная работа №2. Изучение работы шифраторов и дешифраторов..... | 7  |

| Лабораторная работа №3. Изучение работы регистров.....                 | 10 |

| Лабораторная работа №4. Изучение работы микросхемы памяти.....         | 13 |

Редактор

---

Подписано в печать

Объем п.л.

Формат бумаги 60x84 1/16

Тираж

Заказ №

---

Типография ТашИИТ.

Таш